Merge

将多个信号合并为一个信号

库:

Simulink /

Signal Routing

HDL Coder /

Ports & Subsystems

描述

Merge 模块可将多个输入合并为单个输出。输出值始终等于其驱动模块最近计算的输出。通过设置输入数目参数来指定输入数目。

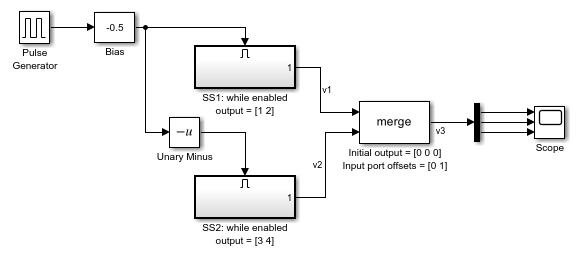

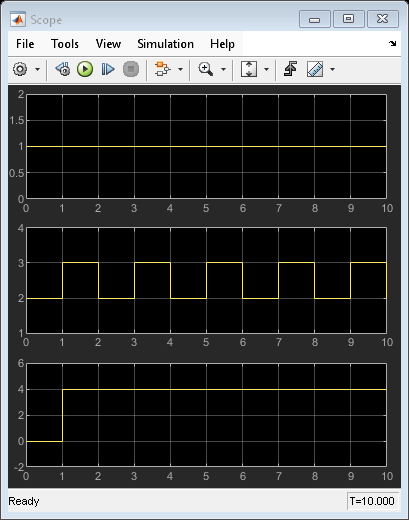

请将一个 Merge 模块用于将在不同时间更新的输入信号交叉成一个合并信号,交叉值在合并信号中保留其各自的身份和时间。要将同时更新的信号合并成数组或矩阵信号,请使用 Vector Concatenate 模块。

Merge 模块的使用原则

使用 Merge 模块时,请遵循以下原则:

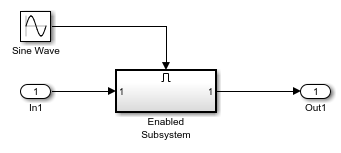

始终使用条件执行子系统来驱动 Merge 模块,而不涉及任何中间模块。

确保在任何时间步都最多只有一个驱动条件执行子系统在执行中。

确保所有输入信号具有相同的采样时间。

不要为 Merge 模块的输入信号创建分支。

不要记录输入到 Merge 模块的信号。

不要指定 Merge 模块的模块执行优先级。有关详细信息,请参阅指定模块执行顺序、执行优先级和标记。

对于驱动 Merge 模块的所有条件执行子系统 Outport 模块,请将禁用时的输出设置为保持。

如果 Model 模块的输出来自 MATLAB Function 模块或 Stateflow® 图,不要将该输出端口连接到 Merge 模块的输入端口。

Merge 模块支持将不同任务中的信号合并到一个根 Outport 模块。

对于一个 Merge 模块的每个输入,最顶层的非虚拟源必须为条件执行子系统(不包括 For Iterator 或 While Iterator 子系统)。

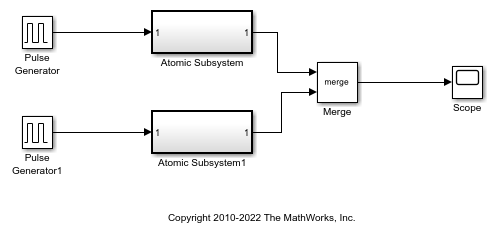

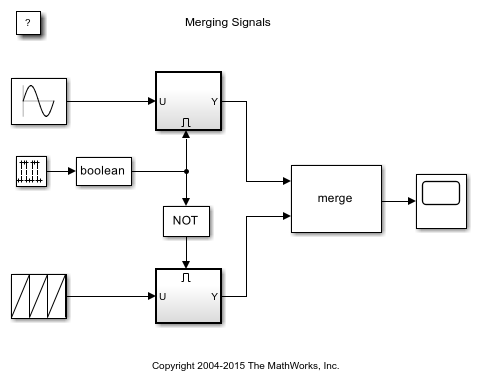

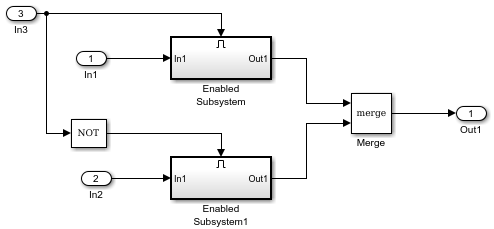

下一个图显示了有效的 Merge 模块用法,它合并来自两个条件执行子系统的信号。

总线支持

Merge 模块支持总线。输入可以是满足下列限制条件的虚拟或非虚拟总线信号:

输入数目必须大于一。

初始输出必须为零、非零标量或有限数值结构体。

必须清除允许端口宽度不等复选框。

所有输入都必须为总线且必须相同(所有元素的层次结构相同,并具有相同的名称和属性)。

Merge 模块的非虚拟总线输入中的所有信号必须具有相同的采样时间。您可以使用 Rate Transition 模块更改总线中单个信号或所有信号的采样时间。

合并 S-Function 输出

对于来自 S-Function 模块的信号,仅当用来存储 S-Function 模块输出的内存可重用时,才能使用 Merge 模块合并该信号。如果某个模型将不可重用的 S-Function 模块端口连接到 Merge 模块,则当您尝试更新或仿真模型时,Simulink® 将显示错误消息。请参阅 ssSetOutputPortOptimOpts。

多任务根输出

连接到一个根 Outport 模块的 Merge 模块允许合并不同任务中的信号,方法是允许这些信号同时写入该根 Outport 模块。源的联合采样时间会赋给该 Merge 模块。

同一任务中的 Merge 模块的所有源均应在条件执行子系统中,且这些子系统不应在同一时间步中同时输出。

示例

扩展示例

限制

所有连接到 Merge 模块的信号在功能上都是同一信号。因此,这些信号必须满足一个给定信号最多只能有一个关联信号对象的限制条件。有关详细信息,请参阅

Simulink.Signal。如果 Merge 模块的输入来自单一发起方,则不会对其执行运行时诊断。例如,单一发起方可以是一个执行连接到 Merge 模块的函数调用子系统的 Stateflow 图。

禁用时,不要将要合并的多个条件执行子系统的输出端口设置为重置。此操作可能导致多个子系统同时更新该模块。尤其是,禁用的子系统通过重置其输出来更新 Merge 模块,而使能子系统通过计算其输出来更新该模块。

为了防止此行为的发生,对于要合并的每个条件执行子系统,请将 Outport 模块参数禁用时的输出设置为保持。

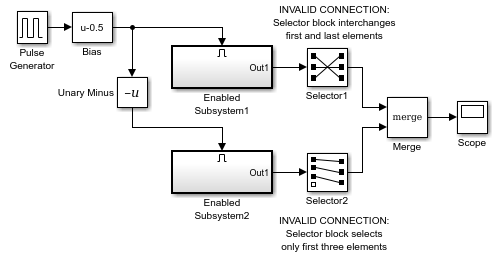

Merge 模块不接受其元素被重新排序或者只有部分元素被选中的输入信号,如下图所示。

不要将已在条件执行子系统外部进行了合并的输入信号连接到模块。

可使用总线数组作为 Merge 模块的输入信号,但存在以下限制:

允许端口宽度不等 - 清除此参数。

初始条件 - 可为此参数指定:

值

0。在这种情况下,总线数组中的每个信号都使用初始值0。结构体数组,为总线数组中的每个信号指定初始条件。

标量结构体,为总线类型定义的每个元素指定初始条件。使用此方法可为数组中的每条总线指定相同的初始条件。

端口

输入

输出

参数

模块特性

数据类型 |

|

直接馈通 |

|

多维信号 |

|

可变大小信号 |

|

过零检测 |

|