Detect Design Errors in Controller Model

To detect hidden design errors in your model early in the verification process, use design error detection analysis. This tutorial shows how to perform design error detection analysis, review the analysis results, and then fix the identified design errors.

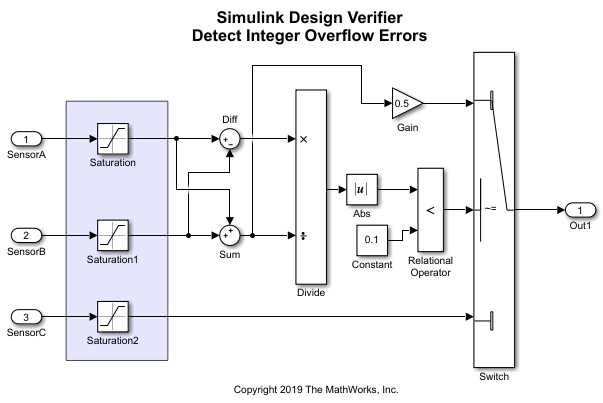

Consider a controller that has three sensor inputs: SensorA, SensorB, and SensorC. The controller algorithm operates according to the equation:

The algorithm is modeled as:

Follow these steps to perform design error detection analysis:

Prepare Model for Design Error Detection

1. Open the model sldvexControllerIntegerOverflow:

sldvexControllerIntegerOverflow

2. On the Apps tab, click the arrow on the right of the Apps section. Under Model Verification, Validation, and Test, click Design Verifier.

3. On the Design Verifier tab, in the Mode section, select Design Error Detection.

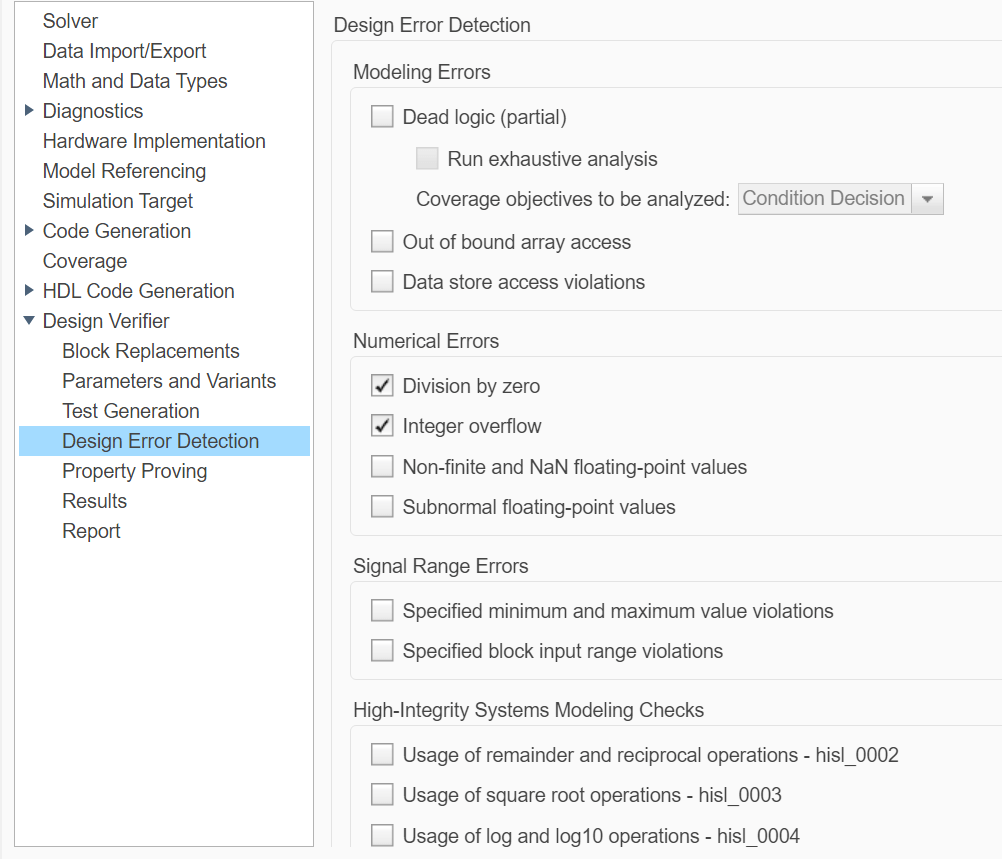

4. Click Error Detection Settings. In the Configuration Parameters dialog box, on the Design Verifier > Design Error Detection pane, clear Defect checker. Select the checks that you want to perform.

5. Click Apply and OK to save the changes.

Perform Design Error Detection Analysis

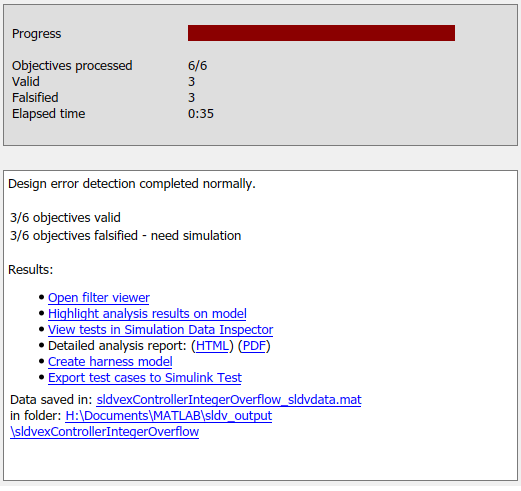

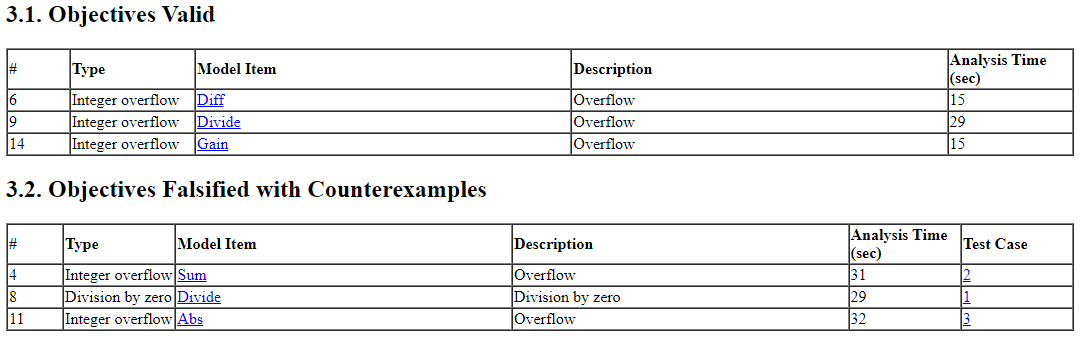

To perform design error detection analysis, on the Design Verifier tab, click Detect Design Errors. The software analyzes the model for design errors and displays the results in the Results window. The results indicate that three out of six objectives were falsified.

Review the Analysis Results

You can review the analysis results by reviewing the analysis report.

Highlight Analysis Results on the Model

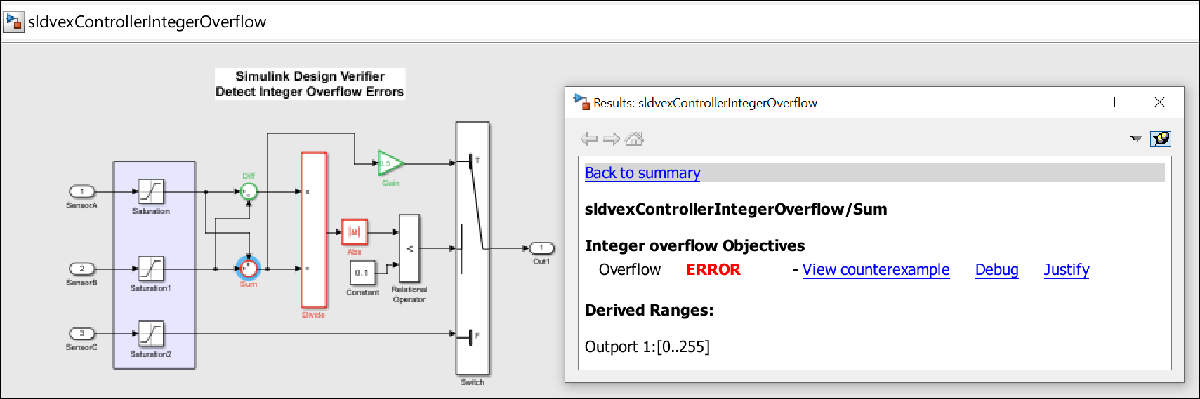

After the analysis is complete, the results are highlighted in the model. To highlight the results manually, on the Design Verifier tab, in the Review Results section, click Highlight in Model.

1. Select the Sum block. The Results window displays the integer overflow objectives of the Sum block.

2. To debug the integer overflow error, click View counterexample. The harness model and the Signal Editor block opens.

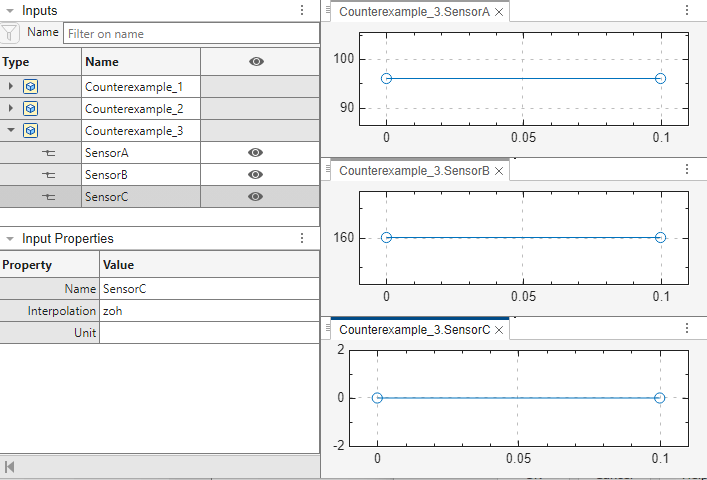

3. Double-click the Signal Editor block to open the Block Parameters dialog box. Select Counterexample_3 as the active scenario from the Active scenario list. Click the Open Signal Editor ![]() to visualize the scenarios.

to visualize the scenarios.

When the input value of CounterExample_3.SensorA is 97 and the input value of CounterExample_3.SensorB is 171, the Sum block output overflows. The accumulator data type of the Sum block is set to an incorrect type uint8, which results in overflow errors and division-by-zero errors on the downstream Divide block.

Review Analysis Report

To view the HTML report, in Review Results, click HTML Report. The Design Error Detection Objectives section lists the objectives of each model items and their description.

Fix Design Errors

In the example, the design error detection analysis found integer overflow and division-by-zero errors in the model. The errors were caused due to a mismatch in the integer data type.

To fix the errors, change the Accumulator data type and Output data type to uint16 to handle the range of possible signal values. Double-click the Sum block, and in the Block Parameters dialog box, set Accumulator data type and Output data type to uint16. When you rerun the design error detection analysis, the Results Summary window reports that six out of six objectives are valid. When you simulate the test case for the Sum block, observe that the test case resolves the error.