什么是设计错误检测?

设计错误检测是指在 Simulink® 模型中识别逻辑错误、死逻辑及其他潜在问题的过程。设计错误检测在初始模型开发阶段及早识别错误期间、模型更新期间以及在实际系统中实现模型之前使用最为有效。在开发过程中及早识别设计错误有助于:

在设计阶段及早检测错误,从而降低开发成本。

改进设计,确保系统行为正确且可预测。

提高安全性,这在汽车和航空航天等安全关键型系统中尤为重要。

具有决策或条件结果的模型对象会接受死逻辑检测。

使用 Simulink Design Verifier 进行设计错误检测分析

设计错误检测分析模式指定用于控制 Simulink Design Verifier™ 如何检测其分析的模型中的运行时错误的选项。您可以在“配置参数”对话框的 Design Verifier 窗格下配置设计错误检测。

在对您的模型进行仿真之前,先在设计错误检测模式下分析您的模型以查找并诊断这些错误。设计错误检测分析会确定导致错误的条件,帮助您识别可能的设计缺陷。

设计错误检测模式可检测以下类型的错误:

死逻辑

越界数组访问

整数或定点数据溢出

除以零

浮点使用错误(

Inf/NaN 和次正规)超出指定的最小值和最大值的中间信号值

数据存储访问违规

指定的模块输入范围违规

高完整性系统建模检查

要分析您的模型以检测设计错误,请使用以下工作流:

验证您的模型是否与 Simulink Design Verifier 软件兼容。

指定用于控制 Simulink Design Verifier 如何检测您的模型中的设计错误的选项。

要检测常见的设计错误,请使用缺陷检查器。

执行 Simulink Design Verifier 分析。

查看分析结果。

分析完成后,您可以:

点击各个模块以查看该模块的分析结果。

创建包含演示错误的测试用例的框架模型。

创建包含整个模型的详细结果的分析报告。

了解设计错误检测分析结果

当您运行设计错误检测分析时,默认情况下,软件会以四种颜色之一突出显示模型对象,以便于您查看分析结果。

| 模型对象突出显示颜色 | 分析结果 |

|---|---|

绿色 | 以下两种情况:

|

红色 | 以下至少一种情况:

|

橙色 | 对于至少一个目标,分析无法确定模型对象是否具有死逻辑或其他设计错误之一。在以下情况下,可能会发生这种情况:

|

灰色 | 模型对象不是分析的一部分。 |

钢蓝色 | 此模型对象的所有目标都是使用分析过程中提供的过滤器文件排除或申述的。 |

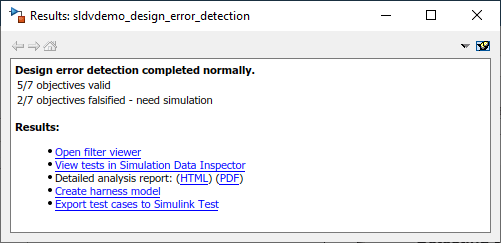

Simulink Design Verifier 的“结果”窗口在初始时会显示分析结果的摘要。默认情况下,Simulink Design Verifier 的“结果”窗口始终是最顶部的可见窗口。要更改此设置,请点击 ![]() 图标,然后在上下文菜单中清除始终在顶部旁边的复选标记。

图标,然后在上下文菜单中清除始终在顶部旁边的复选标记。

当您点击模型中的某个对象时,Simulink Design Verifier 的“结果”窗口中会显示关于该对象的结果的更多详细信息。

在“结果摘要”窗口中查看最新的分析结果

如果您关闭分析结果以修复模型中错误的原因,则可能需要再次查看分析结果。只要您的模型保持不变,您就可以在“结果摘要”窗口中查看最新的分析结果。

要查看最新结果,请在 Design Verifier 选项卡的查看结果部分中,点击结果摘要。

对于任何 Simulink Design Verifier 分析,您都可以通过“结果摘要”窗口执行以下任务:

打开过滤器资源管理器。

在模型上突出显示分析结果。

在仿真数据检查器中查看测试。

生成详细分析报告。

创建框架模型,或者在框架模型已经存在的情况下打开它。请注意,如果没有目标被证伪或满足,则无法创建框架模型。

将测试用例导出到 Simulink Test。

查看数据文件。

查看日志文件。