检测数据存储访问违规

Simulink® Design Verifier™ 设计错误检测分析可识别在仿真中发生的意外数据存储读写序列。分析检测到这些数据存储访问冲突:

写前读

读后写

写后写

要检测模型中的数据存储访问冲突:

在 Design Verifier 选项卡的模式部分中,选择设计错误检测。

点击错误检测设置。

在“配置参数”对话框的 设计错误检测窗格中,选择 数据存储访问违规。点击确定。

点击检测设计错误。

分析完成后,软件会突出显示带有分析结果的模型,并且“结果摘要”窗口会显示分析摘要。

检测模型中的数据存储访问冲突

此示例显示如何检测数据存储访问冲突并查看分析结果。sldvexDataStoreAccessViolations 示例模型由定义 alpha 和 beta 数据存储的 Data Store Memory 模块组成。在示例模型中,Write Subsystem 使用 Data Store Write 模块将数据写入数据存储,而 Read Subsystem 使用 Data Store Read 模块从数据存储中读取数据。

打开模型

在命令提示符下,输入:

open_system('sldvexDataStoreAccessViolations');

配置分析选项以检测数据存储访问冲突

该模型已预先配置数据存储访问冲突参数设置为 On。

执行设计错误检测分析

在 Design Verifier 选项卡上,点击检测设计错误。Simulink Design Verifier 分析数据存储访问冲突模型。分析完成后,“结果摘要”窗口将显示一个目标被证伪。

查看分析结果

该模型通过分析结果得到重点强调。

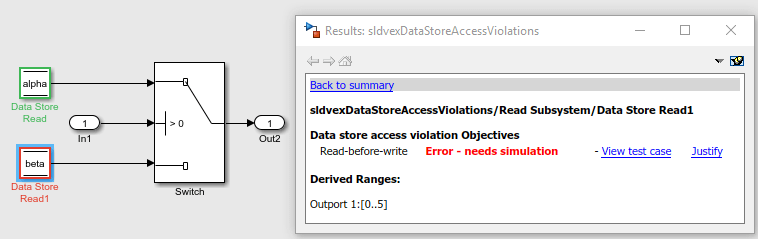

(1)打开 Read Subsystem 并点击红色高亮显示的 Data Store Read1 模块。结果检查器窗口显示违反数据存储访问顺序的“写前读”目标。

(2) 要查看复制该错误的测试案例,请点击查看反例。框架模型窗口和信号编辑器对话框打开,显示测试用例。

(3) 要仿真测试用例,在框架模型窗口中,点击运行仿真。仿真完成后,诊断查看器窗口将显示以下警告消息:

The block 'sldvexDataStoreAccessViolations_harness/Test Unit (copied from sldvexDataStoreAccessViolations)/Read Subsystem/Data Store Read1' is reading from the data store 'sldvexDataStoreAccessViolations_harness/Test Unit (copied from sldvexDataStoreAccessViolations)/Data Store Memory1' before any blocks have written to this entire region of memory at time 0.0. For performance reasons, occurrences of this diagnostic for this memory at other simulation time steps will be suppressed.

修复数据存储访问冲突错误

写前读目标会导致错误,因为在执行读取操作之前尚未将模块写入 beta 数据存储。

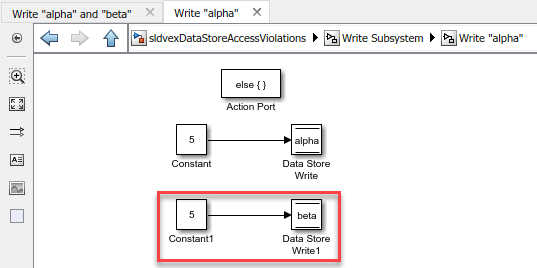

打开 Write Subsystem 并双击 Write "alpha"。在 Write "alpha" 子系统中,只有 alpha 数据存储写入了常量值。因此,“beta”Data Store Read 模块发生了写前读数据存储访问冲突。

要修复该错误,请在 Write "alpha" 子系统中添加一个 Constant 模块,并使用 Data Store Write 模块将其值写入 beta 数据存储(下图中突出显示)。

在 Design Verifier 选项卡上,点击检测设计错误。分析完成后,软件会报告所有目标均有效。

限制

由初始化逻辑产生的对数据存储的读取和写入不会检查是否存在违规。例如,在检查数据存储访问冲突时,初始化函数中发生的初始化逻辑会被忽略。对于初始化外部或内部调用的任何类型的逻辑,都会分析与初始化无关的行为。

从 Reset、reinitialize 和/或 terminate 函数生成的数据存储中读取和写入的数据不会被检查是否违反规则。