死逻辑检测

死逻辑表示在仿真过程中无法激活的模型元素。死逻辑检测可识别无法发生的决策覆盖率和条件覆盖率结果。在某些情况下,死逻辑是由于设计中的错误引起的。在仿真模型之前,可使用死逻辑检测来分析模型以检测是否存在死逻辑。在 Simulink® Design Verifier™ 中,死逻辑的设计错误检测包括以下两个分析选项:

死逻辑(部分):如果您选择此选项,Simulink Design Verifier 会在不进行任何逼近(例如浮点数的有理逼近或 While 循环逼近)的情况下分析您的模型。有关详细信息,请参阅近似值在模型分析中的作用。使用此选项,Simulink Design Verifier 不会报告活动逻辑或未决目标,并且可能无法识别模型中的某些死逻辑。

可在以下位置使用此选项:

模型顾问中。请参阅使用模型顾问检查设计错误。

在“配置参数”对话框的 Design Verifier > 设计错误检测窗格中。

运行穷举分析:使用此选项,Simulink Design Verifier 除了报告死逻辑和未决目标外,还会报告活动逻辑。在某些情况下,此选项可识别或发现其他死逻辑。分析可能会使用逼近,并相应地进行报告。

此选项位于“配置参数”对话框的 Design Verifier > 设计错误检测窗格中。

运行部分检查以检测死逻辑

如果您未使用模型顾问,要检测死逻辑,请执行以下操作:

在 Design Verifier 选项卡的模式部分中,选择设计错误检测。

点击错误检测设置。

在“配置参数”对话框的 Design Verifier > 设计错误检测窗格中:

要应用这些设置,请点击确定并关闭“配置参数”窗口。

点击检测设计错误。

运行穷举分析以检测死逻辑

运行死逻辑分析并查看结果

此示例说明如何检测 sldvSlicerdemo_dead_logic 示例模型中的死逻辑。死逻辑检测在模型中查找导致模型元素保持非活动状态的不可达目标。

打开

sldvSlicerdemo_dead_logic模型。openExample('slcheck/AnalyzeTheDeadLogicExample',... 'supportingFile','sldvSlicerdemo_dead_logic');

在 Design Verifier 选项卡的模式部分中,选择设计错误检测。

点击错误检测设置。

在“配置参数”对话框的 Design Verifier > 设计错误检测窗格中:

点击检测设计错误。

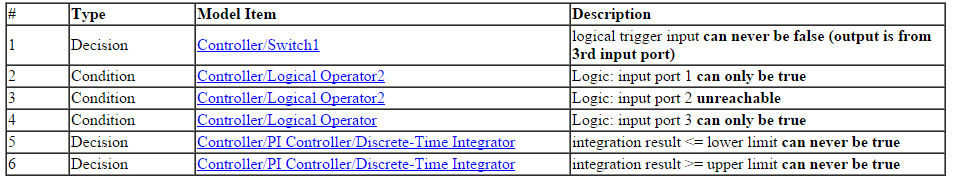

软件会分析模型以检测死逻辑,并在“结果摘要”窗口中显示结果。结果表明,

32个目标中有10个被发现是死逻辑。

点击在模型上突出显示分析结果。死逻辑模型元素会以红色突出显示。

打开

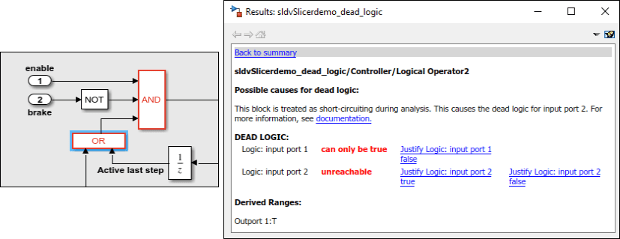

Controllersubsystem,然后点击以红色突出显示的 OR 模块。结果检查器会显示死逻辑的摘要。set输入等于1,因此 OR 模块的input port 1只能为 true。状态表明input port 1的 false 条件是死逻辑。同样,input port 2为unreachable,因为目标永远不会执行并且是死逻辑。

要查看详细的分析报告,请在“结果摘要”窗口中点击 HTML。

报告会显示模型中所有死逻辑结果的摘要。

死逻辑

软件会将详细分析结果存储在管理 Simulink Design Verifier 数据文件的

DeadLogic字段中。您可以使用数据文件对结果进行进一步分析。

建议:

您可以按照以下步骤使用模型切片器来查找可能对特定模块产生影响的参数:

a.使用模型切片器创建一个 SLSlicerAPI.ParameterDependence 对象。

slicerObj = slslicer('sldvSlicerdemo_dead_logic');

pd = slicerObj.parameterDependence;b.查找影响 Discrete-Time Integrator 模块的参数。

param = parametersAffectingBlock(pd, 'sldvSlicerdemo_dead_logic/Controller/PI Controller/Discrete-Time Integrator');

上图显示了函数 parametersAffectingBlock 返回的参数,这些参数对 Discrete-Time Integrator 模块有影响。可以考虑对该函数返回的参数进行调节。

c.执行清理以退出模型的编译状态。

slicerObj.terminate;