Generate FPGA User Logic with AXI4-Stream Video Interface

This example shows how to select an AXI4-Stream Video interface for your generated FPGA user logic.

This example follows the same workflow, and models and generates HDL code for the same edge detection and overlay algorithm, as the Developing Vision Algorithms for Zynq-Based Hardware example. However, this example generates the FPGA user logic with an AXI4-Stream Video interface rather than the Vision HDL Toolbox™ pixel streaming interface.

The workflow is the same until the HDL code generation steps. Then, in the HDL code generation section, this example shows how to select the AXI4-Stream Video interface for your FPGA user logic. Using this interface enables you to integrate the generated code into a larger design that uses AXI4-Stream interface.

The workflow in this example applies when you use an HDMI FMC card. When you use a MIPI FMC card, the reference design uses AXI4-Stream Video interface by default.

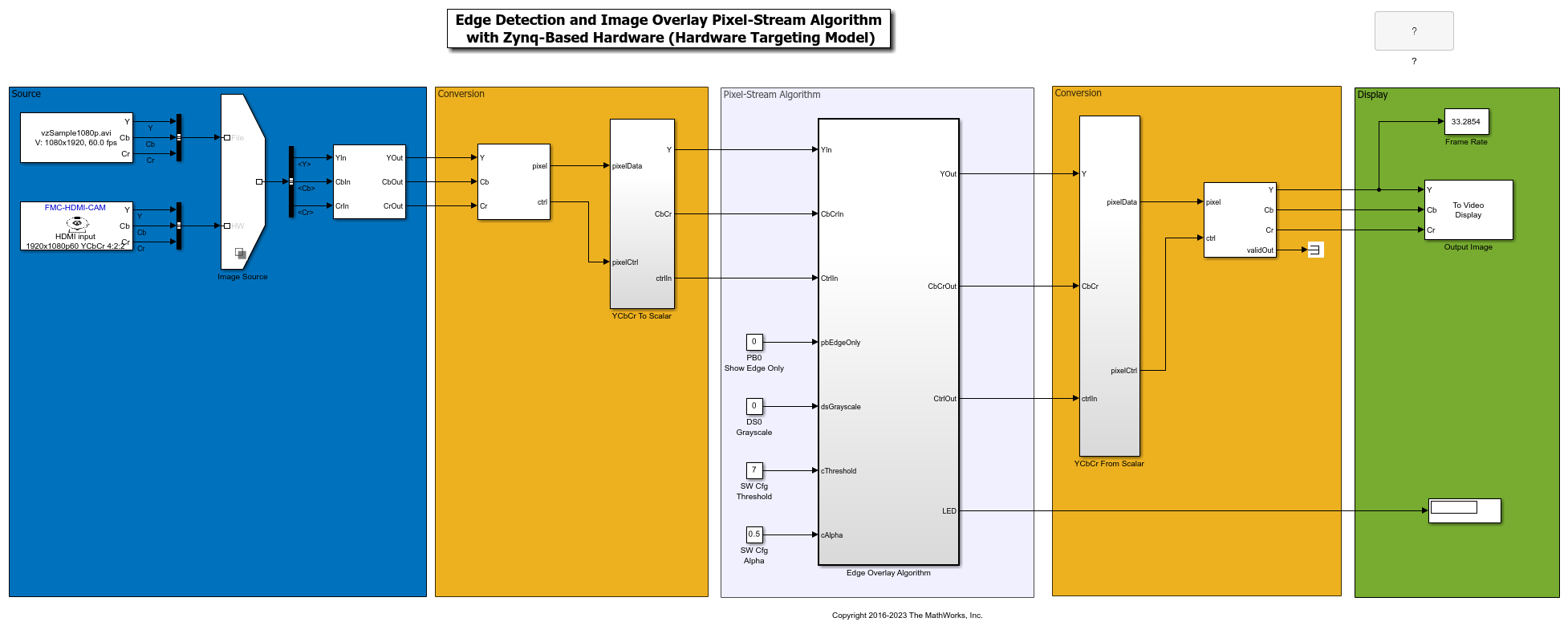

Pixel-Stream Model

This model provides a pixel-stream implementation of the algorithm for targeting HDL. Instead of working on full images, the HDL-ready algorithm works on a pixel-streaming interface.

open_system('vzEdge_03_TargetSource')

The source video for this example comes from either the From Multimedia File block, which reads video data from a multimedia file, or from the Video Capture HDMI block, which captures live video frames from an HDMI source connected to the Zynq®-based hardware. To configure the source, right-click the variant selection icon in the lower-left corner of the Image Source block, and set Active Variant to either File or HW.

The Stream format parameter of the Video Capture HDMI block is set to Pixel-stream video to match the default FPGA image. The default image has pass-through user logic and uses the Vision HDL Toolbox™ pixel streaming protocol.

For details of the inputs to the edge detection algorithm, see the Developing Vision Algorithms for Zynq-Based Hardware example.

close_system('vzEdge_03_TargetSource',0)

Target the Algorithm

After you are satisfied with the pixel streaming algorithm simulation, you can target the pixel algorithm to the FPGA on the Zynq board.

Start the targeting workflow by right-clicking the Edge Overlay Algorithm subsystem and in the HDL Coder app section, click the HDL Workflow Advisor button.

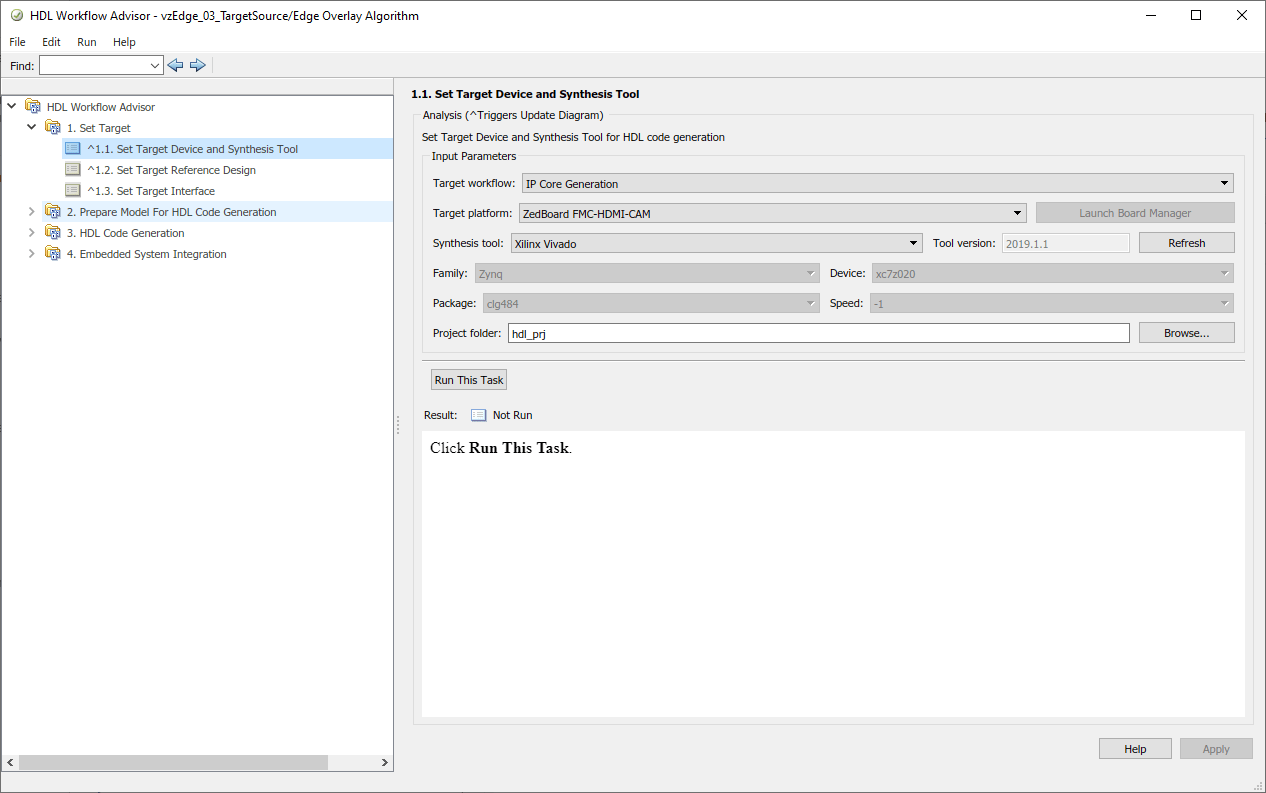

In Step 1.1, select the

IP Core Generationworkflow and select your target platform from the list.

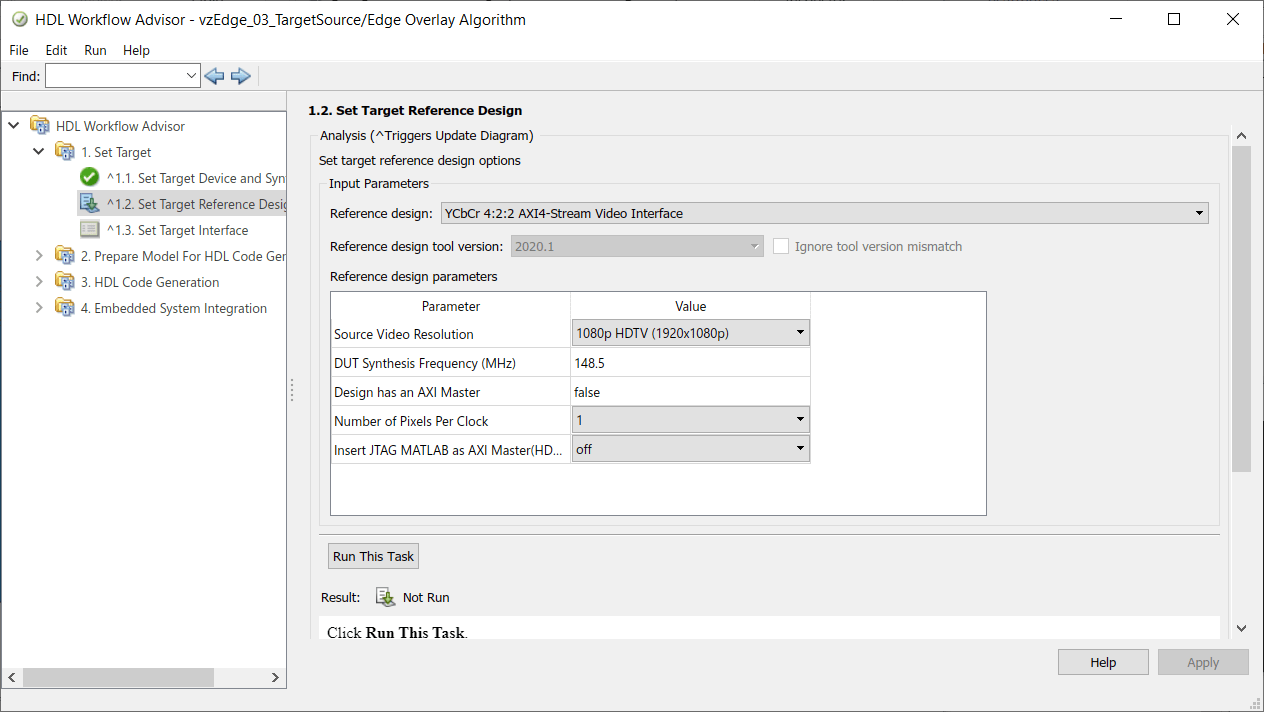

In Step 1.2, select the

YCbCr 4:2:2 AXI4-Stream Video Interfacereference design to match the pixel format of theEdge Overlay Algorithmsubsystem and to enable the AXI4-Stream Video interface on the FPGA user logic.

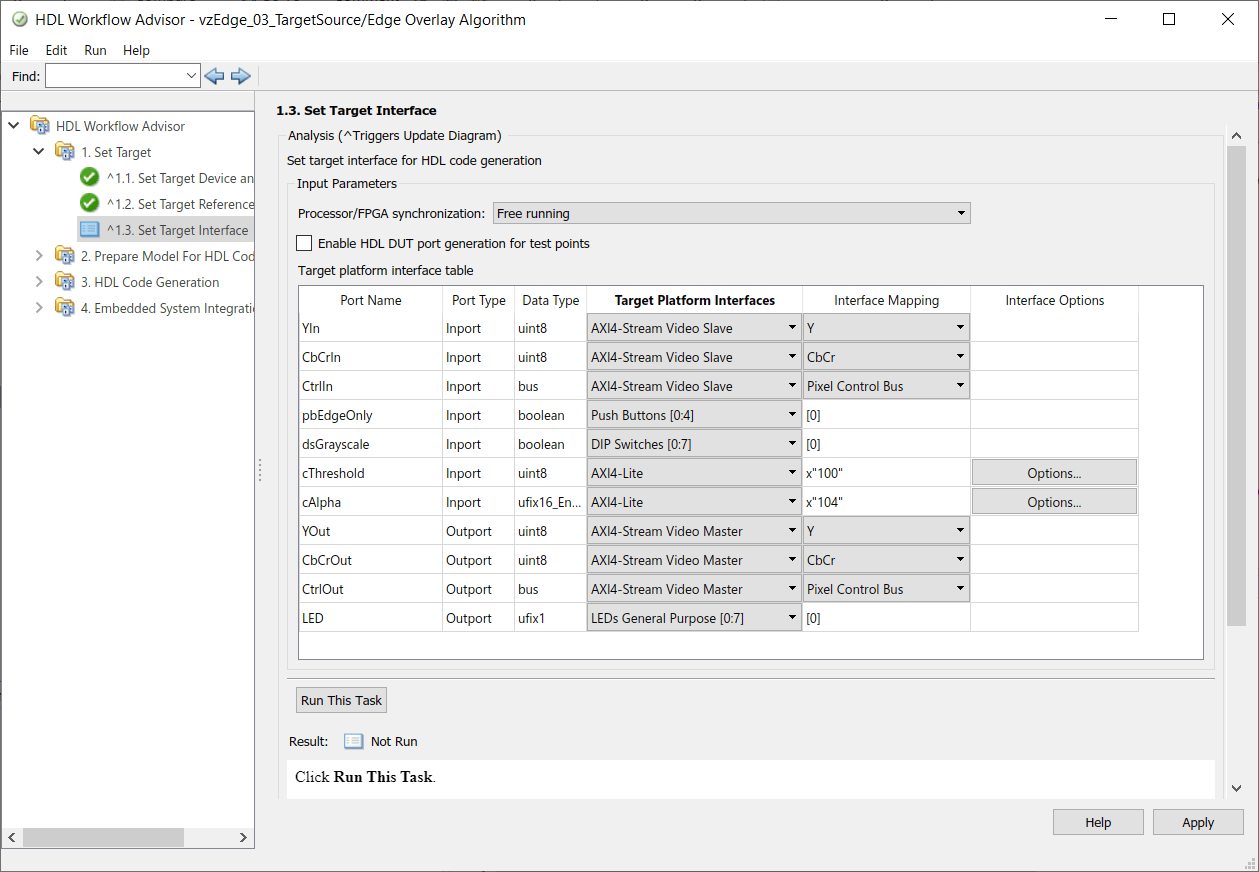

In Step 1.3, map the target platform interfaces to the input and output ports of your design.

The options in the Target Platform Interfaces column vary depending on the pixel format. The figure shows the interface table when you select YCbCr 4:2:2 AXI4-Stream Video Interface. In Target platform interface table, map the YIn, CbCrIn, and CtrlIn ports to AXI4-Stream Video Slave in the Target Platform Interfaces column. Then, select Y, CbCr, and Pixel Control Bus, respectively, in the Interface Mapping column.

Similarly, map the YOut, CbCrOut, and CtrlOut ports to the AXI4-Stream Video Master, and select Y, CbCr, and Pixel Control Bus in the Interface Mapping column.

To use the external interfaces on the target hardware platform, map the accordingly.

pbEdgeOnlyport to push button 0dsGrayScaleport to dip switch 0LEDport to LED 0cAlphaandcThresholdto AXI4-Lite for software control

The AXI4-Stream Video interface communicates in manager and subordinate mode, where the manager device sends data to the subordinate device. If a data port is an input port, assign the port to an AXI4-Stream Video Slave interface, and if a data port is an output port, assign the port to an AXI4-Stream Video Master interface.

Step 2 checks that the design is valid for code generation.

Step 3 generates HDL code for the IP core.

Step 4 integrates the newly generated IP core into the larger Vision Zynq reference design.

Execute each step in sequence to experience the full workflow. Alternatively, if you are already familiar with preparation and HDL code generation phases, right-click Step 4.1 in the left pane and select Run to selected task.

In Step 4.2, the workflow generates a targeted hardware interface model and, if the Embedded Coder® Support Package for AMD SoC Devices is installed, a Zynq software interface model. Click Run this task to run with the default settings.

Steps 4.3 and 4.4

The rest of the workflow generates a bitstream for the FPGA, downloads the bitstream to the target, and reboots the board.

To reload your bitstream to the board later, call

downloadImage(vz,'FPGAImage','C:\work\hdl_prj\vivado_ip_prj\mydesign_axi.bit', ... 'DeviceTree','visionzynq-zedboard-hdmicam-axi-video.dtb');

The device tree files ship with the software and the file names indicate the board and the interface used by the FPGA user logic. The interface configuration of the bitstream and the device tree must match. In this example, the Step 4.1 copies the matching dtb file to hdl_prj\vivado_ip_prj\sdcard\visionzynq-zedboard-hdmicam-axi-video.dtb.

Generated Models from HDL Workflow Advisor

Step 4.2 generated two or four models depending on whether Embedded Coder® is installed. The models are a 'targeted hardware interface' model and it associated library model, and a 'software interface' model and its associated library model. You can use the 'targeted hardware interface' model to control the reference design from the Simulink® model without Embedded Coder. The 'software interface' model supports full software targeting to the Zynq device when the Embedded Coder product and Embedded Coder Support Package for AMD SoC Devices are installed, enabling external mode simulation, processor-in-the-loop simulation, and full deployment.

The Video Capture HDMI blocks in the generated hardware and software models have the Streaming interface parameter set to whichever interface you chose in HDL Workflow Advisor Step 1.2. In this example, Streaming interface is set to AXI4-stream video. This parameter is read-only in the generated models.

Targeted Hardware Interface Model

In this model, you can adjust the configuration of the reference design and read or drive control ports of the hardware user logic. These configuration changes affect the design while it is running on the target. You can also display captured video from the target device.

Software Interface Model

In this model, you can run in external mode to control the configuration of the reference design and read or drive any control ports of the hardware user logic that you connected to AXI-Lite registers. These configuration changes affect the design while it is running on the target. You can use this model to fully deploy a software design. This model is generated only if the Embedded Coder product and the Embedded Coder Support Package for AMD SoC Devices are installed.