SDR Hardware Architecture

A software-defined radio (SDR) is a wireless device that typically consists of a configurable RF front end with an FPGA or programmable system-on-chip (SoC) to perform digital functions. SDR hardware architectures can transmit and receive signals at different frequencies to implement wireless standards such as FM radio, wireless local area network (WLAN), LTE, and 5G.

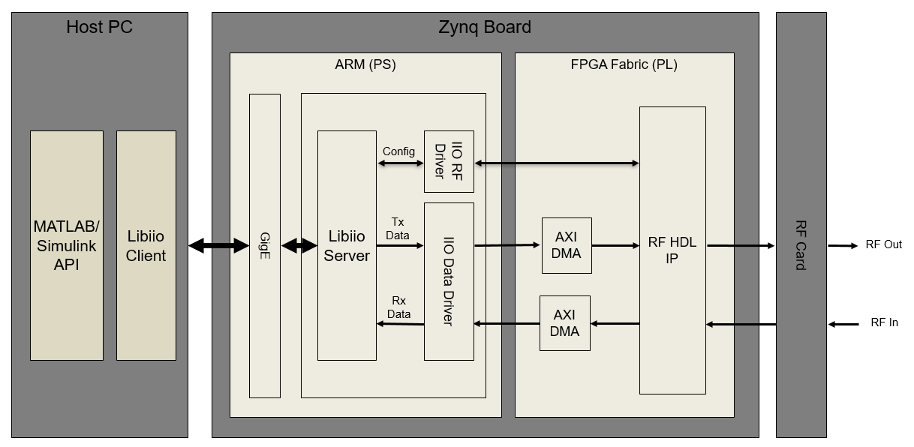

The SoC Blockset™ Support Package for AMD FPGA and SoC Devices provides preconfigured MathWorks® Linux® and FPGA images that you can use to configure your SDR for host-radio communication in MATLAB® or Simulink®. This illustration is a conceptual overview of how the support package integrates SDR capabilities on the underlying Zynq® hardware architecture, common to each supported SDR hardware device. For a list of supported SDR hardware devices, see Hardware Support.

The MathWorks Linux image uses the Analog Devices® libiio library for configuring the RF chip and for handling host-radio data movements. The library provides interfacing with Linux industrial I/O (IIO) devices. On the embedded platform, the libiio interface is available through the Libiio Server running on Linux. In MATLAB or Simulink, the libiio interface is available through the Libiio Client. The Libiio Server and Client use a built-in Ethernet protocol for communication. The library also enables C code generation from Simulink models that can run on the ARM processor directly interacting with the radio device.