Implement on Hardware

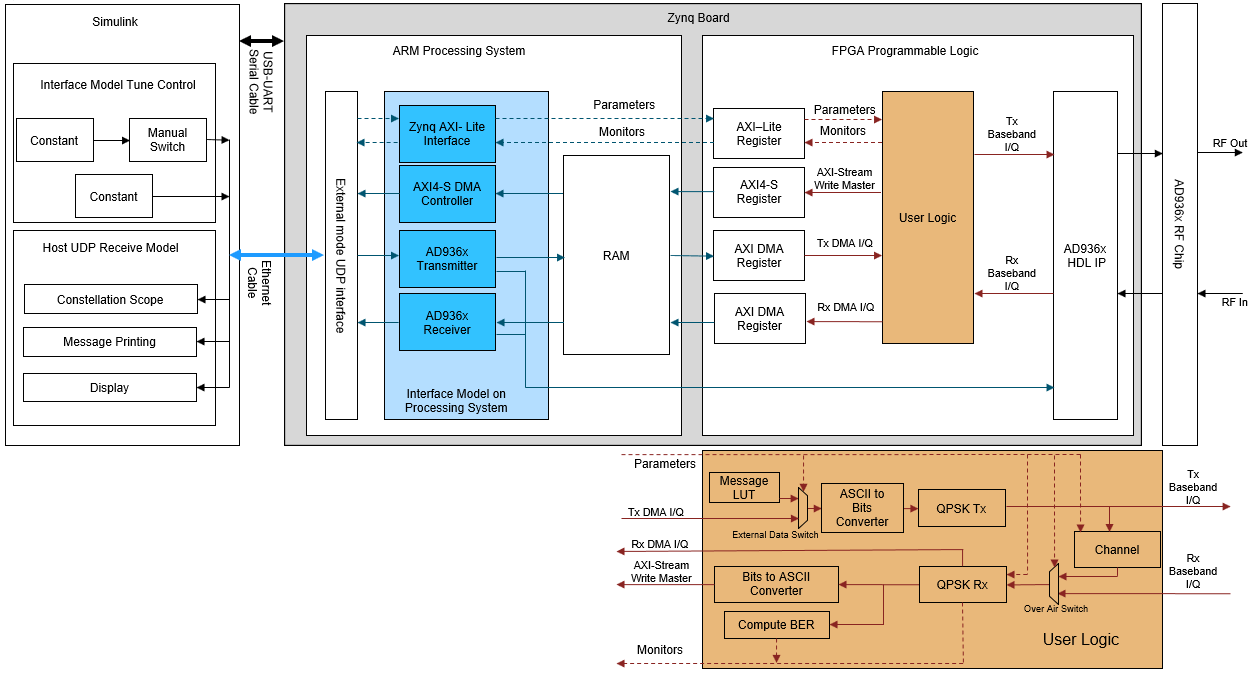

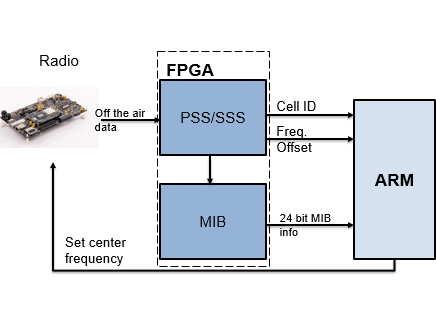

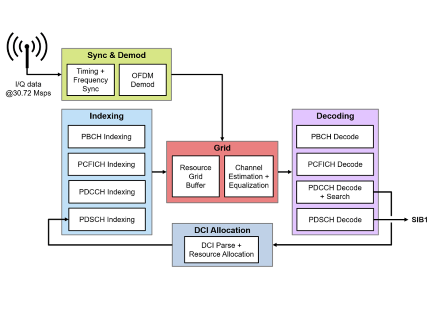

You can design an SDR algorithm in Simulink®, and then prototype your design on the AMD Zynq-based radio hardware. You can either deploy a hardware-software (HW/SW) co-design implementation partitioned between the ARM® processor and the FPGA fabric of the underlying system on chip (SoC), or prototype the design targeting the FPGA fabric only. The workflow is available in Simulink only.

Functions

sdrdev | Create radio object for interfacing with Xilinx Zynq-based radio hardware |

downloadImage | Download SD card image or bitstream file |

Objects

comm.SDRDevAD936x | Interface with AD936x-based Zynq radio hardware |

comm.SDRDevFMCOMMS5 | Interface with FMCOMMS5 Zynq radio hardware |

Blocks

| AD936x Transmitter | Send data to AD936x-based Zynq radio hardware (Since R2024b) |

| AD936x Receiver | Receive data from AD936x-based Zynq radio hardware (Since R2024b) |

| FMCOMMS5 Transmitter | Send data to FMCOMMS5 Zynq radio hardware |

| FMCOMMS5 Receiver | Receive data from FMCOMMS5 Zynq radio hardware |

Topics

- Hardware-Software Co-Design Overview

Learn the basics of the hardware-software co-design feature in this support package and its software requirements.

- Installation for Hardware-Software Co-Design

Install and configure additional support packages and third-party tools required by hardware-software co-design workflow.

- Hardware-Software Co-Design Workflow

Deploy partitioned hardware-software co-design implementations for SDR algorithms.

- Guidelines for Configuring the Software Interface Model

Configure your model for continuous and packet-based transmission and reception.

- System Timing

Explore ARM processor scheduler options for the software interface model.

- FPGA Targeting Workflow

Prototype SDR algorithms on the FPGA fabric only.

Troubleshooting

Troubleshooting Hardware-Software Co-Design

Resolve issues encountered while using the hardware-software co-design workflow.