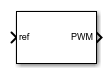

PWM Generator (Multilevel)

生成用于模块化多电平转换器的脉冲宽度调制信号或波形

库:

Simscape /

Electrical /

Control /

Pulse Width Modulation

描述

PWM Generator (Multilevel) 模块实现用于模块化多电平转换器的脉冲宽度调制 (PWM) 发生器。PWM 技术通过在满功率传输和无功率传输之间快速切换,来控制从一个电气组件到另一个电气元件的功率传输。

模块根据功率子模块的数量和两种转换器拓扑(半桥和全桥)计算模块化多电平转换器的栅极脉冲。您可以分别使用功率子模块数和转换器拓扑参数来指定功率子模块的数量和转换器拓扑。

端口

输入

输出

参数

版本历史记录

在 R2020b 中推出