Access FPGA External Memory Using AXI Manager

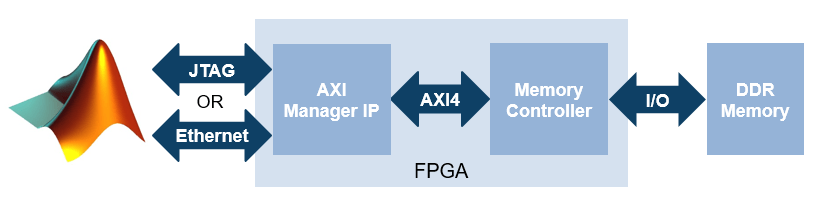

This example shows how to use AXI manager to access external DDR memories connected to an FPGA. The FPGA design instantiates an Intel® DDR memory controller for accessing the DDR memories. This memory controller provides a memory-mapped subordinate interface for read and write operations from the FPGA. The AXI manager feature provides an AXI manager IP that allows MATLAB® to access any memory-mapped subordinate IPs in the FPGA. In this example, we demonstrate how to integrate the JTAG AXI manager IP or Ethernet AXI manager IP into a Qsys design, and then read and write the DDR memory from MATLAB.

Requirements

Intel Quartus® Prime software with a supported version listed in Supported EDA Tools and Hardware

Intel Arrow® DECA MAX® 10 FPGA development kit

HDL Verifier™ Support Package for Intel FPGA Boards

USB-Blaster II™ download cable

Ethernet cable

Set Up for Using JTAG AXI Manager

Step 1: Set up FPGA board. Make sure that the DECA board is connected to the host computer via the USB JTAG cable.

Step 2: Prepare example in MATLAB

Set up the Intel Quartus Prime tool path. Use your own Intel Quartus Prime installation path when executing the command.

hdlsetuptoolpath('ToolName','Altera Quartus II', ... 'ToolPath','C:\intelFPGA\18.0\quartus\bin64\quartus.exe');

Create a Quartus project for this example. This tcl script creates the Quartus project, and adds the design files to the project.

system('quartus_sh -t create_project_deca.tcl')

This command takes a few seconds to finish. When it is done, a Quartus project named "aximaster_deca.qpf" is created in your current directory.

Step 3: Configure Quartus Prime project to use AXI manager

Copy the IP to the project directory using the following command.

setupAXIManagerForQuartus('aximaster_deca.qpf')

Open the generated Quartus project in GUI mode. You can double-click the project in a file browser, or execute this command in MATLAB.

system('quartus aximaster_deca.qpf &')

Step 4: Inspect JTAG AXI manager IP in Qsys design (optional)

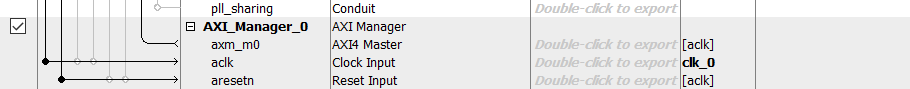

In the Quartus GUI, open the Qsys design file, system.qsys, and inspect how the AXI Manager IP is connected to the DDR controller.

Step 5: Generate FPGA programming file and program FPGA

To generate the FPGA programming file , click the "Start Compilation" button in Quartus Prime.

After generating the programming file, program the FPGA in MATLAB using the following command.

filProgramFPGA('Altera','output_files/aximaster_deca.sof',1)

Set Up for Using Ethernet AXI Manager

Step 1: Set up FPGA board. Make sure that the DECA board is connected to the host computer via both the USB Blaster II download cable and the Ethernet cable.

Step 2: Prepare example in MATLAB

Set up the Intel Quartus Prime tool path. Use your own Intel Quartus Prime installation path when executing the command.

hdlsetuptoolpath('ToolName','Altera Quartus II', ... 'ToolPath','C:\intelFPGA\18.0\quartus\bin64\quartus.exe');

Create a Quartus project for this example. This tcl script would create the Quartus project, and add the design files we created to the project.

system('quartus_sh -t create_project_eth_deca.tcl')

When it is done, a Quartus project named "eth_aximaster_deca.qpf" is created in your current directory.

Step 3: Configure Quartus Prime project to use the Ethernet AXI manager

Copy the IP to the project directory using the following command.

setupAXIManagerForQuartus('eth_aximaster_deca.qpf')

Open the generated Quartus project in GUI mode. Double-click the project in a file browser, or execute this command in MATLAB.

system('quartus eth_aximaster_deca.qpf &')

Step 4: Inspect Ethernet AXI manager IP in Qsys design (optional)

In the Quartus GUI, open the Qsys design file, aximaster.qsys, and inspect how the UDP AXI Manager IP is connected to the DDR controller.

The Ethernet-based AXI manager IP has been assigned a target IP address of 192.168.1.2 and UDP port value of 50101. These values can be changed by double clicking on the ethernet_mac_hub_IP in Qsys.

Step 5: Generate FPGA programming file and program FPGA

To generate the FPGA programming file, click the "Start Compilation" button in Quartus Prime.

After generating the programming file, program the FPGA in MATLAB using the following command.

filProgramFPGA('Altera','output_files/eth_aximaster_deca.sof',1)

Read and Write Operations to the FPGA

After programming the FPGA, you can read and write into the AXI subordinate connected to the AXI manager IP. In this example, the data will be written to the DDR memory connected to the FPGA, and retrieved back into MATLAB.

Create the AXI manager object in MATLAB.

If using JTAG AXI manager:

h = aximanager('Intel')

If using Ethernet AXI manager:

h = aximanager('Intel','interface','PLEthernet','deviceAddress','192.168.1.2','port','50101');

Run these two commands to write a single word of value 100 into DDR memory at address 0 and read it back by using the AXI manager object.

writememory(h,0,100) readmemory(h,0,1)

You can also read and write large vectors of data into DDR memory using a single read/write command in MATLAB. These commands automatically break down the large amount of data into smaller bursts so that they can be transferred via AXI4 protocol. The function uses the largest possible burst size for each burst to maximize the throughput performance. The following commands write 100000 words into DDR memory and read them back. It also checks if the read back data are correct and reports the execution time.

address = 0; data = 1:100000; writememory(h,address,data); r = readmemory(h,address,100000); assert(all(r==data));

See Also

aximanager | writememory | readmemory