HDL Code Generation and Deployment

Vision HDL Toolbox™ provides libraries of blocks and System objects that support HDL code generation. To generate HDL code from these designs, you must have an HDL Coder license. HDL Coder also enables you to generate scripts and test benches for use with third-party HDL simulators.

If you have an HDL Verifier license, you can use the FPGA-in-the-loop feature to prototype your HDL design on an FPGA board. The blocks on this page provide efficiency improvements for streaming pixel data across the Simulink® to FPGA board interface. HDL Verifier also enables you to cosimulate a Simulink model with an HDL design running in a third-party simulator.

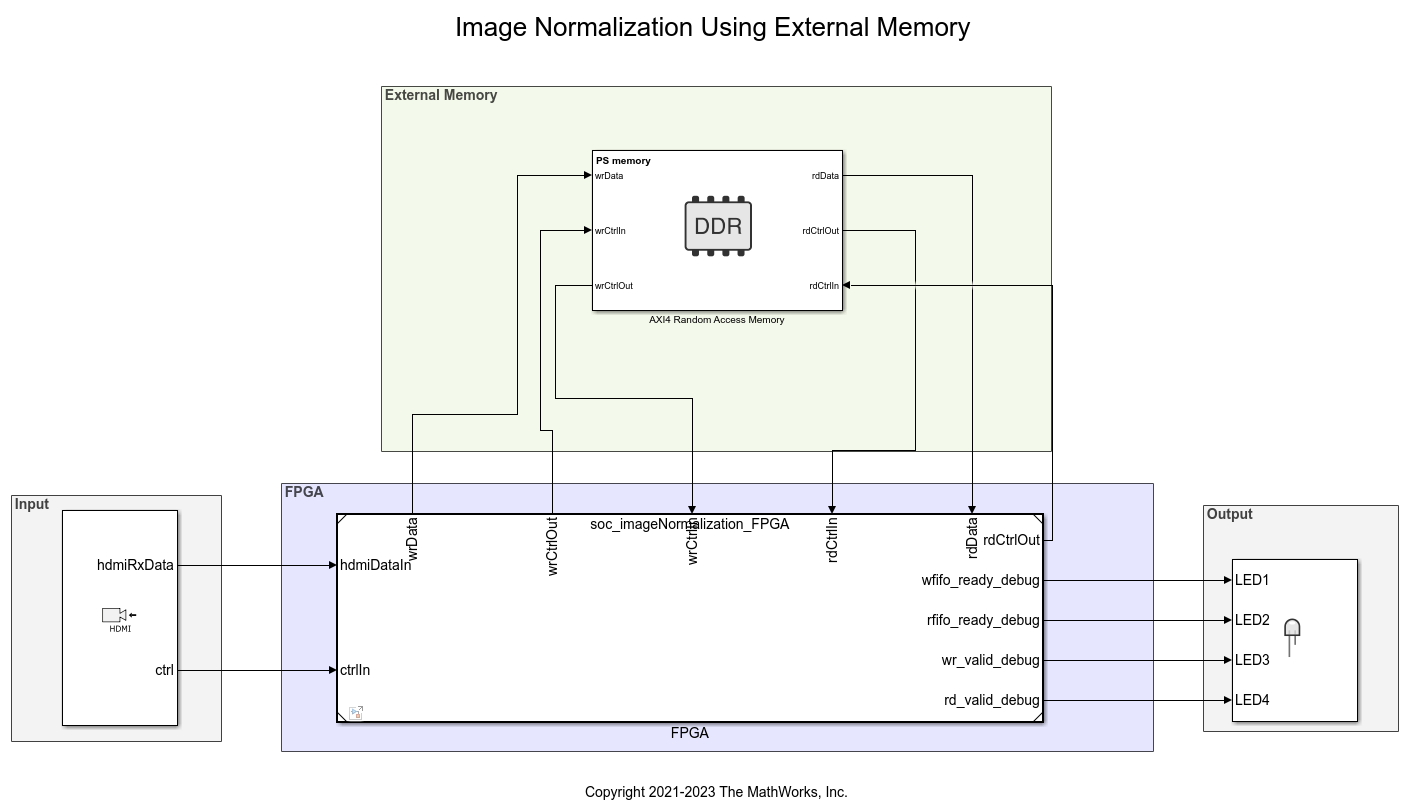

Using SoC Blockset™ and SoC Blockset Support Package for AMD FPGA and SoC Devices features, you can model hardware interfaces, capture live video to your model, and prototype your vision algorithms on Zynq®-based hardware.

Blocks

| FIL Frame To Pixels | Convert frame-based video to pixel stream for FPGA-in-the-loop |

| FIL Pixels To Frame | Convert pixel stream from FPGA-in-the-loop to frame-based video |

Functions

visionhdlsetup | Set up model parameters for HDL code generation for streaming video |

Topics

HDL Code Generation

- HDL Code Generation from Vision HDL Toolbox

Generate HDL code from MATLAB® code and Simulink models.

Verification and Deployment

- HDL Cosimulation

Cosimulate designs in MATLAB or Simulink with third-party HDL simulators. - FPGA-in-the-Loop

Real-time design verification with FPGAs. - Prototype Vision Algorithms on Zynq-Based Hardware

Prototype Vision HDL Toolbox designs on Zynq boards using support packages. - Modeling External Memory

You can model external memory using features from SoC Blockset.

Deploying from Frame-Based Model

- Frame-Based Optical Flow Deployment with LK method

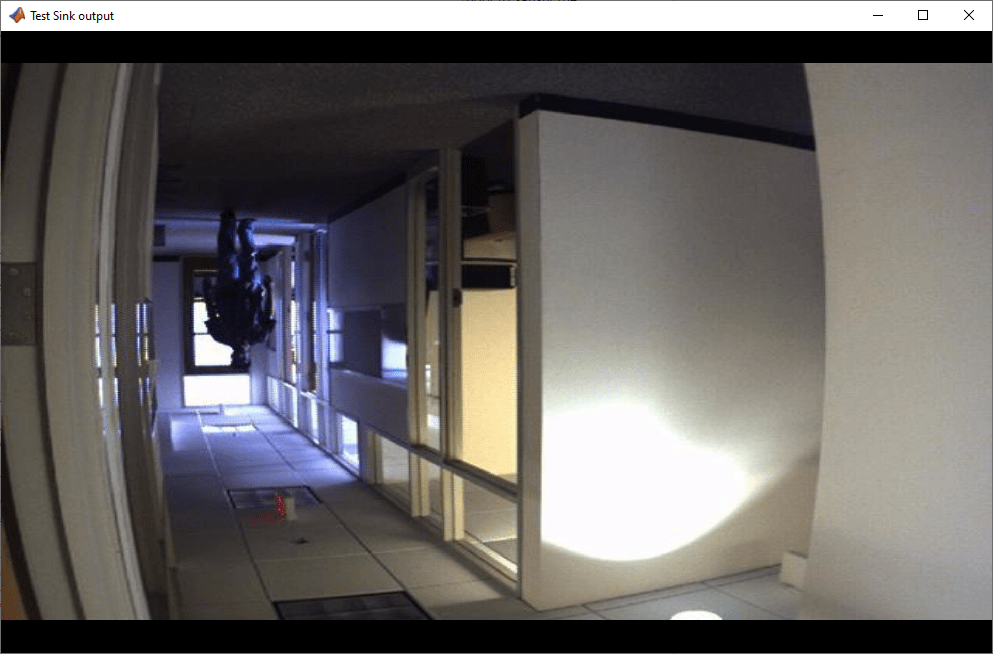

Model a frame-based optical flow algorithm and deploy to hardware. - Frame-Based Video Pipeline Using Zynq UltraScale+ and FMC-HDMI-CAM

Model and deploy a frame-based design that uses HDMI camera input video. - Frame-Based Video Pipeline Using Zynq UltraScale+ and USB Camera

Model and deploy a frame-based design that uses USB camera input video.

Deep Learning

- Deploy and Verify YOLO v2 Vehicle Detector on FPGA

Deploy a you only look once (YOLO) v2 vehicle detector on FPGA and verify the end-to-end application using MATLAB. - Debug YOLO v2 Vehicle Detector on FPGA

Debug a vehicle detector design by viewing internal signals while the design is deployed on a board. - Integrate YOLO v2 Vehicle Detector System on SoC

Simulate a YOLO v2 vehicle detection algorithm that contains FPGA and ARM sections for deployment to an SoC device. - YOLO v2 Vehicle Detector with Live Camera Input on Zynq-Based Hardware

Deploy a YOLO v2 vehicle detection algorithm to the FPGA and ARM® processor on an SoC device and process live HDMI video input.