DVB-S2 HDL PL Header Recovery

This example shows how to implement DVB-S2 time, frequency, and phase synchronization and PL header recovery using Simulink® blocks that are optimized for HDL code generation and hardware implementation.

Digital Video Broadcasting Satellite Second Generation (DVB-S2) modems operate in C (4-8 GHz), Ku (12-18 GHz) and Ka (26-40 GHz) frequency bands. According to the DVB-S2 standard, the satellite transponder bandwidth ranges from 1 MHz to 72 MHz. The model in this example operates at a symbol rate of 25 Mbaud with a root raised cosine (RRC) filter roll-off factor of 0.35. For a MATLAB® implementation of end-to-end DVB-S2 receiver, see the DVB-S2 Link Simulation with RF Impairments and Corrections (Satellite Communications Toolbox) example.

This example shows how to design a DVB-S2 HDL receiver synchronization and physical layer (PL) header recovery system that can handle radio frequency (RF) impairments. The model in this example performs symbol timing synchronization, frame synchronization, coarse and fine frequency synchronization, phase offset estimation and correction, gain correction, and noise variance estimation. Then the model decodes the PL header information followed by fine phase synchronization.

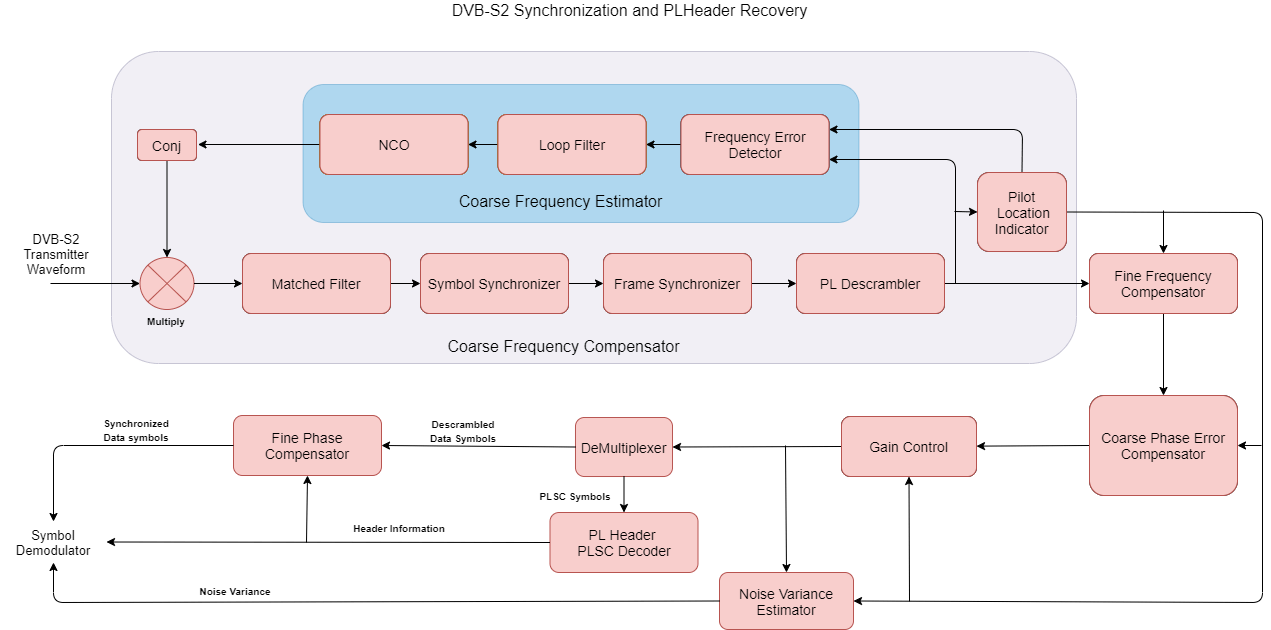

Model Architecture

This section explains the high-level architecture of the model. The model receives the DVB-S2 transmitter waveform sequence that streams into the Coarse Frequency Compensator block. The Symbol Synchronizer block extracts the modulated symbol sequence from the Matched Filter block output and the Frame Synchronizer block locates the start of each frame in the modulated symbol sequence. The PL Descrambler block descrambles the scrambled data symbols and the Pilot Generator block indicates the pilot locations in the frame synchronized sequence. The Coarse Frequency Estimator block estimates the frequency offset, which is used to correct the frequency offset in the transmitter waveform sequence at the model input by conjugate multiplication of the estimate. The Fine Frequency Compensator block corrects the residual frequency left in the PL descrambled sequence. The Coarse Phase Error Compensator block corrects the coarse phase deviation in the Fine Frequency Compensator block output sequence. The phase error compensated sequence is magnitude corrected in the Gain Control block and the gain-corrected sequence is used to estimate noise variance. The Demultiplexer divides the gain-corrected sequence into physical layer signaling code (PLSC) symbols and descrambled data symbols in each frame. The PL Header PLSC Decoder block decodes header parameters MODCOD and FECFrame. The Fine Phase Compensator block uses the MODCOD parameter and corrects the residual phase in the descrambled data symbols that stream into the symbol demodulator.

This block diagram shows the high-level architecture of the model.

File Structure

This example uses two Simulink models, six MATLAB files, and one Simulink data dictionary.

dvbs2hdlPLHeaderRecovery.slx— Top-level Simulink model.dvbs2hdlSyncPLHeaderRecoveryCore.slx— Model reference that synchronizes time, frequency, and phase, and decode PL Header.getdvbs2LDPCParityMatrices.m— Download the LDPC matrices.matfile.dvbs2hdlRxParameters.m— Generate parameters for thedvbs2hdlSyncPLHeaderRecoveryCore.slxmodel reference.dvbs2hdlPhaseNoise.m— Introduce phase noise to the input sequence.dvbs2hdlRxInit.m— Generate the transmitter waveform and initialize thedvbs2hdlSyncPLHeaderRecoveryCore.slxmodel reference.dvbs2hdlStreamRecovery.m— Decode baseband frame (BBFRAME).dvbs2hdlPLHeaderRecoveryVerify.m— Gather PL header parameters and XFECFRAME symbols, demodulate symbols, decode FEC (LDPC and BCH), recover baseband frame, and compute bit errors using Satellite Communications Toolbox functions.dvbs2hdlReceiverData.sldd— Store bus signal configurations that come out of the model reference.

System Interface

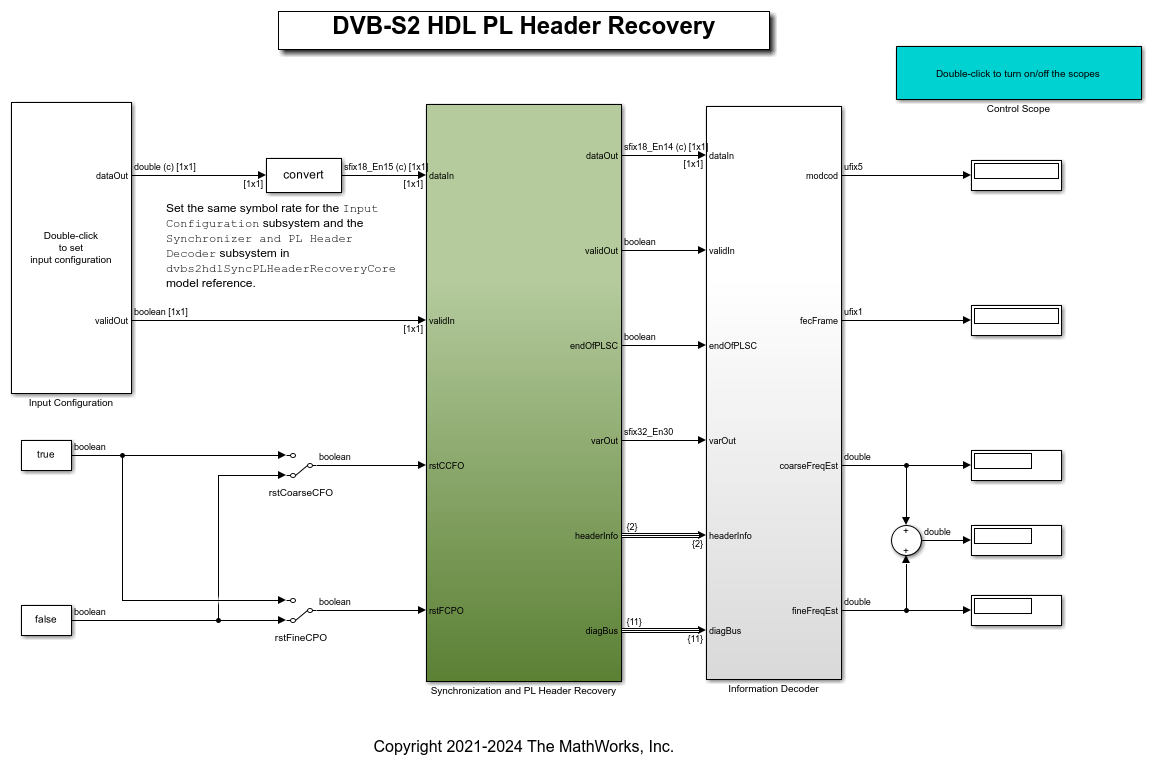

This figure shows the top-level overview of the dvbs2hdlPLHeaderRecovery.slx model.

Model Inputs

dataIn — Input data, specified as an 18 bit complex data with a sample rate that is four times the symbol rate.

validIn — Control signal to validate the dataIn input port, specified as a Boolean scalar.

rstCCFO — Control signal to reset the coarse frequency compensation loop, specified as a Boolean scalar.

rstFCPO — Control signal to reset the fine phase compensation loop, specified as a Boolean scalar.

rstSS — Control signal to reset the symbol synchronizer loop, specified as a Boolean scalar.

Model Outputs:

dataOut — Decoded output symbols, returned as an 18 bit complex scalar.

validOut — Control signal to validate the dataOut output port, specified as a Boolean scalar.

endOfPLSC — Control signal to indicate the end of PLSC symbols in each synchronized frame, specified as a Boolean scalar.

nVar — Estimated noise variance, returned as a 32 bit complex scalar.

headerInfo — Bus signal to provide the parameters MODCOD and FECFrame of the PL header in each synchronized frame.

diagBus — Bus signal to provide the coarse frequency normalized with the sample rate, the fine frequency normalized with the symbol rate, the symbol synchronized output, the PLSC symbols, and the pilot symbols.

Model Structure

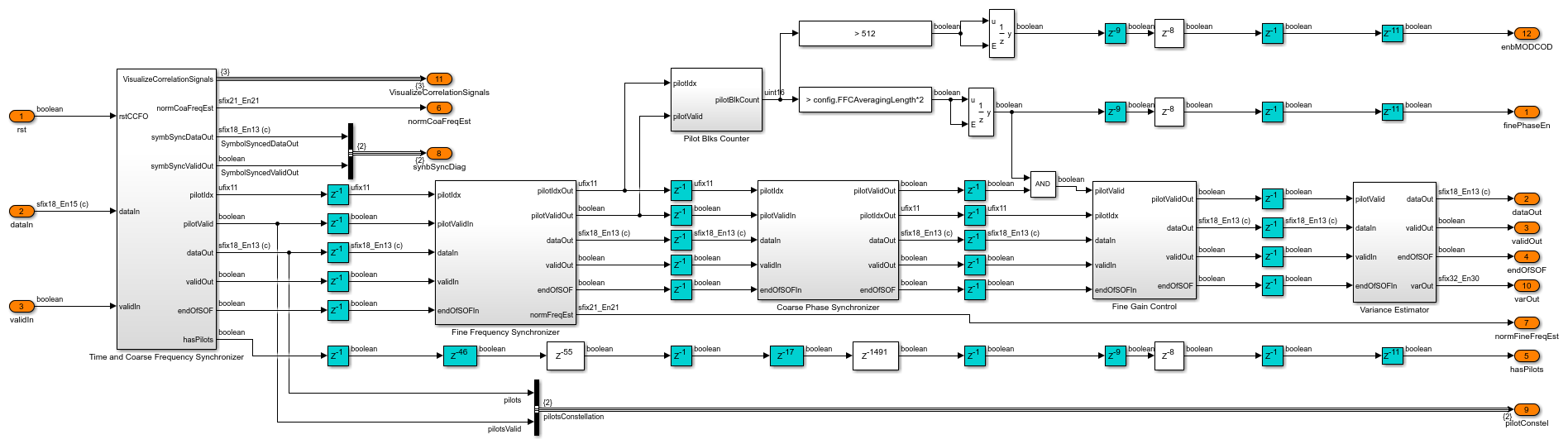

This figure shows the top-level model of the Synchronization and PL Header Recovery subsystem. It comprises Time Frequency and Coarse Phase Synchronizer, PL Header Recovery, and Fine Phase Synchronizer subsystems.

Time Frequency and Coarse Phase Synchronizer

The Time Frequency and Coarse Phase Synchronizer subsystem comprises Time and Coarse Frequency Synchronizer, Fine Frequency Synchronizer, Coarse Phase Synchronizer, Fine Gain Control, and Variance Estimator subsystems.

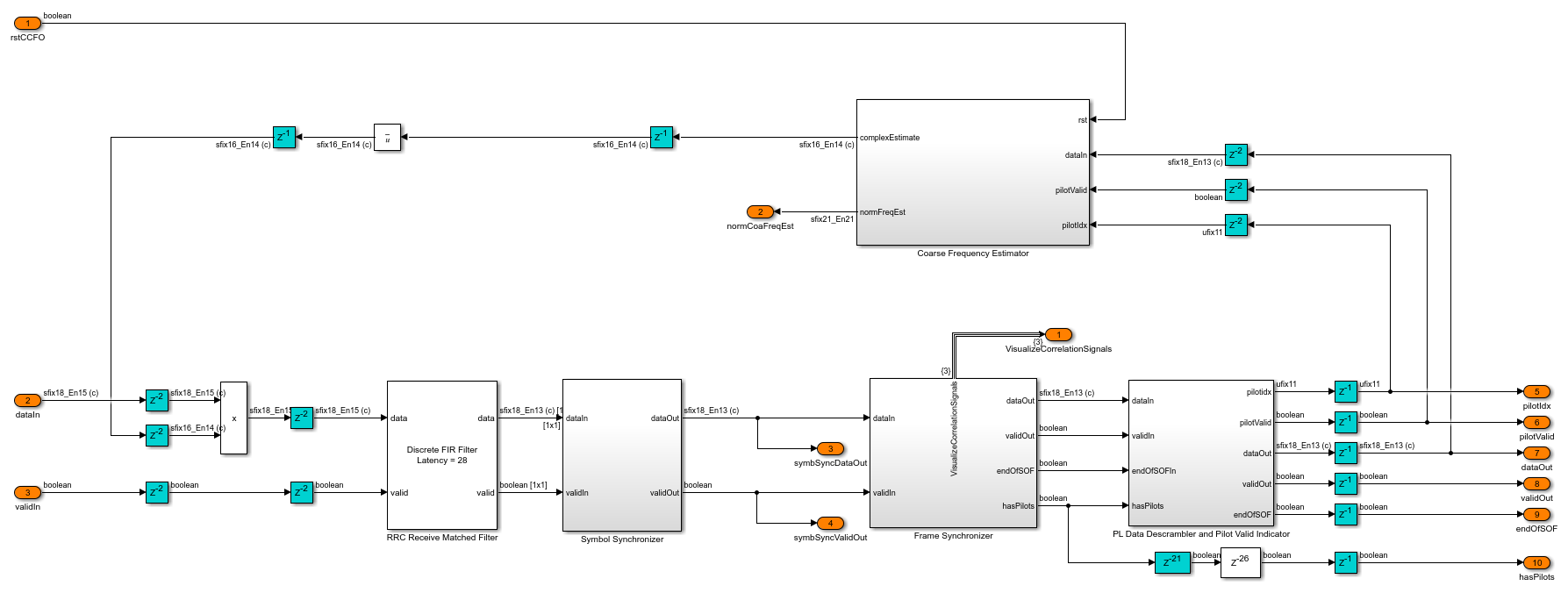

Time and Coarse Frequency Synchronizer

The Time and Coarse Frequency Synchronizer subsystem compensates coarse frequency in a frequency-locked loop (FLL) system. The loop involves RRC matched filtering, symbol synchronization, frame synchronization, PL descrambling, pilot extraction, and coarse frequency estimation.

Coarse Frequency Estimator

The Coarse Frequency Estimator subsystem performs frequency error detection, loop filtering, and direct digital synthesis. The frequency error detection is described with equation C.2 in the Annex C.4 of [ 2 ]. The coarse frequency estimator is a pilot-aided frequency estimator. The Frequency Error Detector subsystem outputs frequency error at the pilot locations. The frequency error is passed through the loop filter and the output of the loop filter drives the NCO block to generate the complex exponential sinusoidal samples. These samples are conjugated and multiplied by the input sequence to correct the frequency offset. The loop filter is disabled for frequency error filtering after 32 pilot blocks so that the estimated frequency remains stable. A reset signal rstCCFO resets the loop filter and restarts the estimation process.

RRC Receive Matched Filter

The RRC Receive Matched Filter is a Discrete FIR Filter block with matched filter coefficients with four samples per symbol, and a roll-off factor of 0.35. The RRC matched filtered output is an RC pulse-shaped waveform that has zero inter symbol interference (ISI) characteristics at the maximum eye opening in the eye diagram of the waveform. Also, the matched filtering process maximizes the signal-to-noise power ratio (SNR) of the filter output.

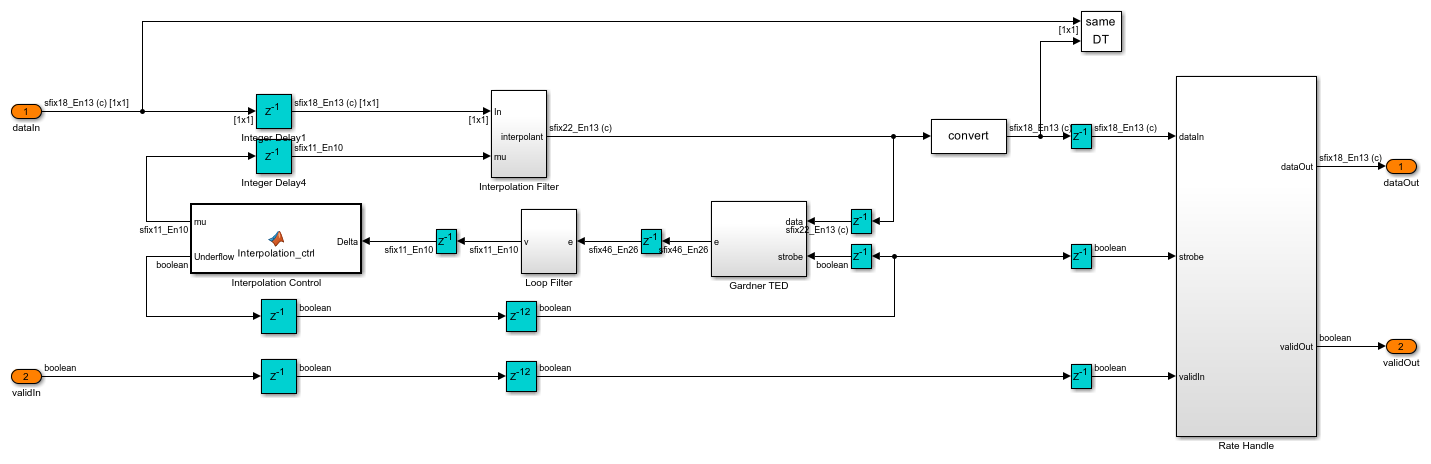

Symbol Synchronizer

The Symbol Synchronizer subsystem is a phase locked loop (PLL) based implementation as described in the chapter 8.4 of [ 4 ]. The subsystem generates one output sample for every four input samples. The PLL loop is set with a normalized loop bandwidth of 8e-3. The Interpolation Filter subsystem implements a piecewise parabolic interpolator with a hardware resource efficient farrow structure. This filter introduces fractional delays in the input waveform. As specified in Annex C.2 of [ 2 ], the Gardner TED subsystem implements a Gardner timing error detector. The loop filter filters the timing error and pass it on to the Interpolation Control MATLAB function block. This block implements a mod-1 decrementing counter to calculate fractional delays based on the loop-filtered timing error to generate interpolants at optimum sampling instants. The Rate Handle subsystem selects the required interpolant indicated by the strobe.

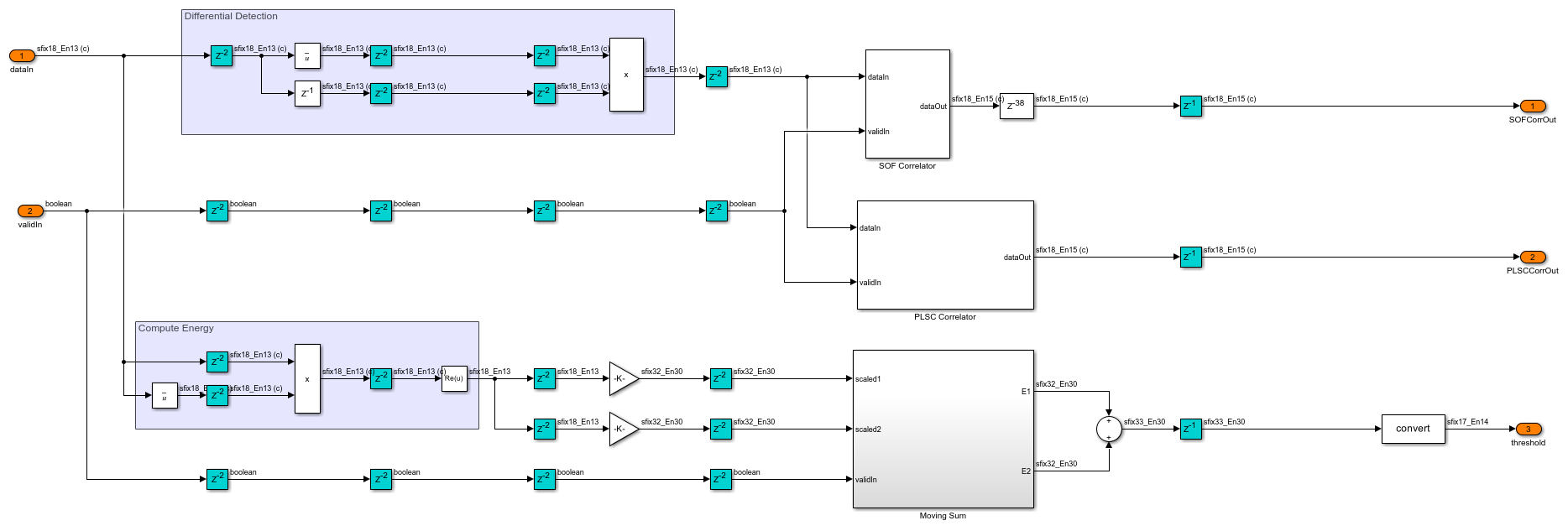

Frame Synchronizer

The frame synchronizer implementation is described in the Annex C.3.1 of [ 2 ]. The Correlator subsystem in the Frame Synchronizer subsystem generates the start of frame (SOF), PLSC correlation values and a threshold. The SOF correlated sequence is delayed by a length of PLSC sequence so that the correlation peaks of SOF and PLSC are aligned. The Pilot and Sync Pulse Indicator subsystem detects the threshold exceeded correlation value and also detects the existence of pilots in the current frame.

The Correlator subsystem implements differential detection and removes the frequency offset dependency in the input sequence. The output sequence is continuously cross-correlated with SOF and PLSC correlators. In addition, the energy of the signal is computed on each time step and then scaled and summed up in the span of each correlator filter length in the Moving Sum subsystem. The scaling factors used before the Moving Sum subsystem are derived from each of the correlation sequences respectively in the dvbs2hdlRxParameters.m file. The two scaled energy values are added to generate a threshold.

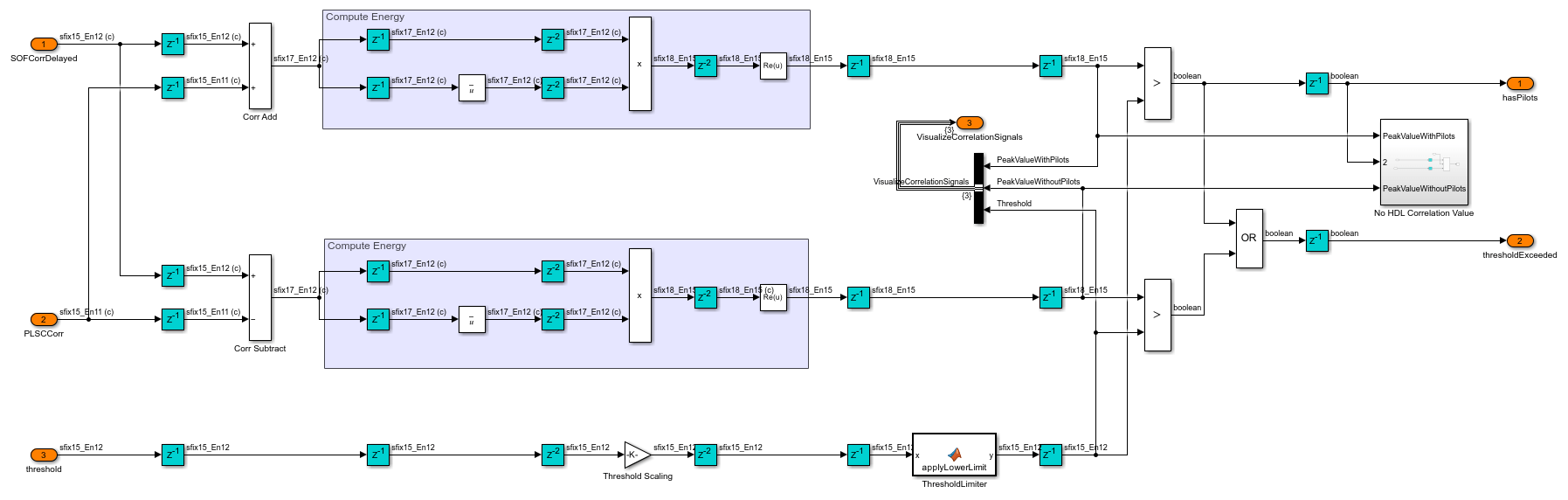

The Pilot and Sync Pulse Indicator subsystem adds and subtracts the SOF and PLSC correlation values and computes energy at each time step to generate two correlation metrics. The threshold is downscaled with a precomputed value in the dvbs2hdlRxParameters.m file, and a lower limit is applied to saturate the threshold with a lower bound. Both of the correlation metrics are compared with the downscaled threshold value. The existence of pilots in the current frame is confirmed if the correlation metric obtained by adding SOF and PLSC correlation values exceeds the downscaled threshold. For a given frame, only one of the two correlation metrics exceeds the threshold based on the existence of pilots.

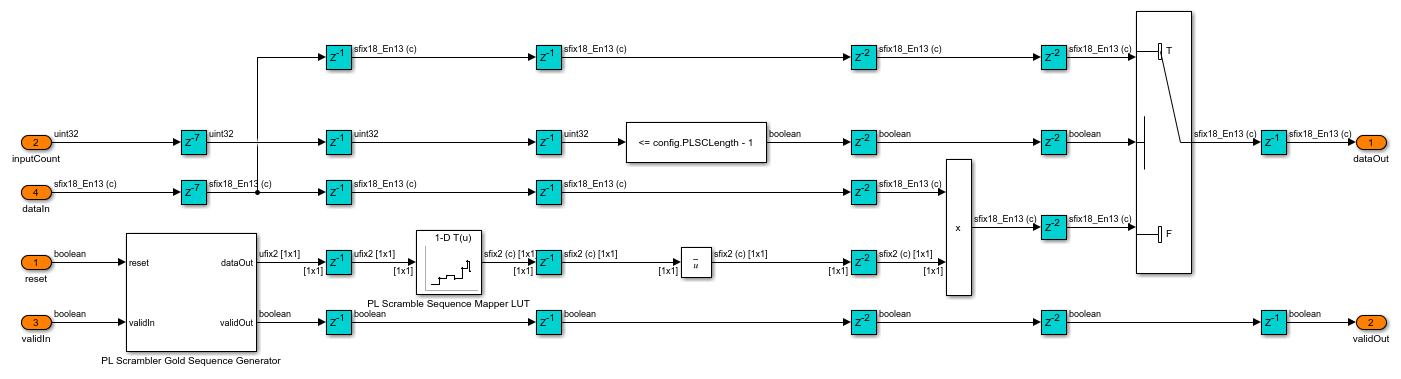

PL Data Descrambler

The PL Data Descrambler subsystem uses PL Scrambler Gold sequence Generator subsystem, which is described in section 5.5.4 of [ 1 ]. The PL Scrambler Gold Sequence Generator subsystem resets for every frame. The gold sequence is used as an address to the PL Scramble Sequence Mapper LUT block to generate the PL scrambling sequence. The scrambling sequence is conjugated to generate the PL descrambling sequence, and the descrambling is performed by multiplying PL descrambling sequence with the input sequence. A switch is used to multiplex the PLSC symbols and the descrambled data symbols.

Pilot Valid Indicator

The Pilot Valid Indicator subsystem counts the input sequence and assigns a pilot index for each symbol. As specified in section 5.5.3 of [ 1 ], the pilots of length 36 symbols exist after 16 slots (1440 symbols) in a pilot-active XFECFRAME (pilot activeness is confirmed in the frame synchronizer). The subsystem generates a pilot valid signal for 36 symbols to indicate the location of the pilot block. The counter resets after the pilot block. This process continues for the rest of the XFECFRAME. The signal, which indicates the end of the PLSC symbols of the next XFECFRAME, determines the end of the current XFECFRAME. The pilot valid signal is not generated after 16 slots if the next XFECFRAME is detected, as the PLSC symbols take the place of pilots.

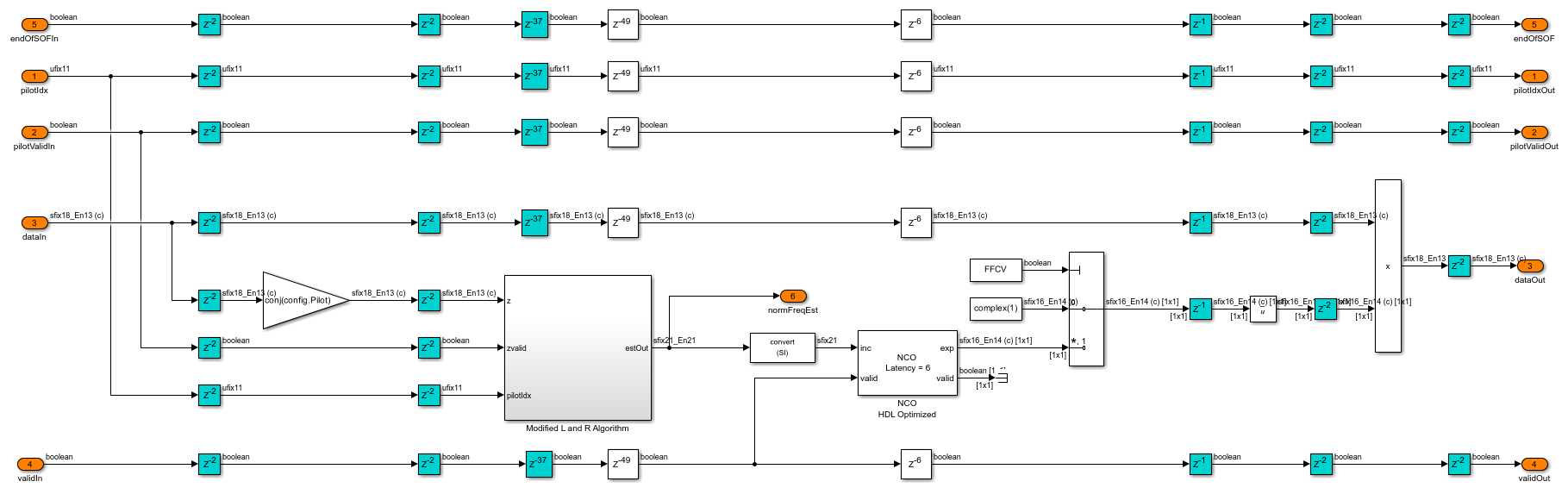

Fine Frequency Synchronizer

The Fine Frequency Synchronizer subsystem uses the Modified L and R algorithm, as described by the equation C.3 in Annex C.4 of [ 2 ]. The L and R algorithm is described in [ 3 ]. The subsystem implements an 18 point autocorrelation function of the L and R algorithm followed by a 512 length moving average filter. The frequency estimate from the Modified L and R Algorithm subsystem drives the NCO block to generate the complex exponential sinusoidal samples, which are conjugated and used to correct the frequency offset in the input.

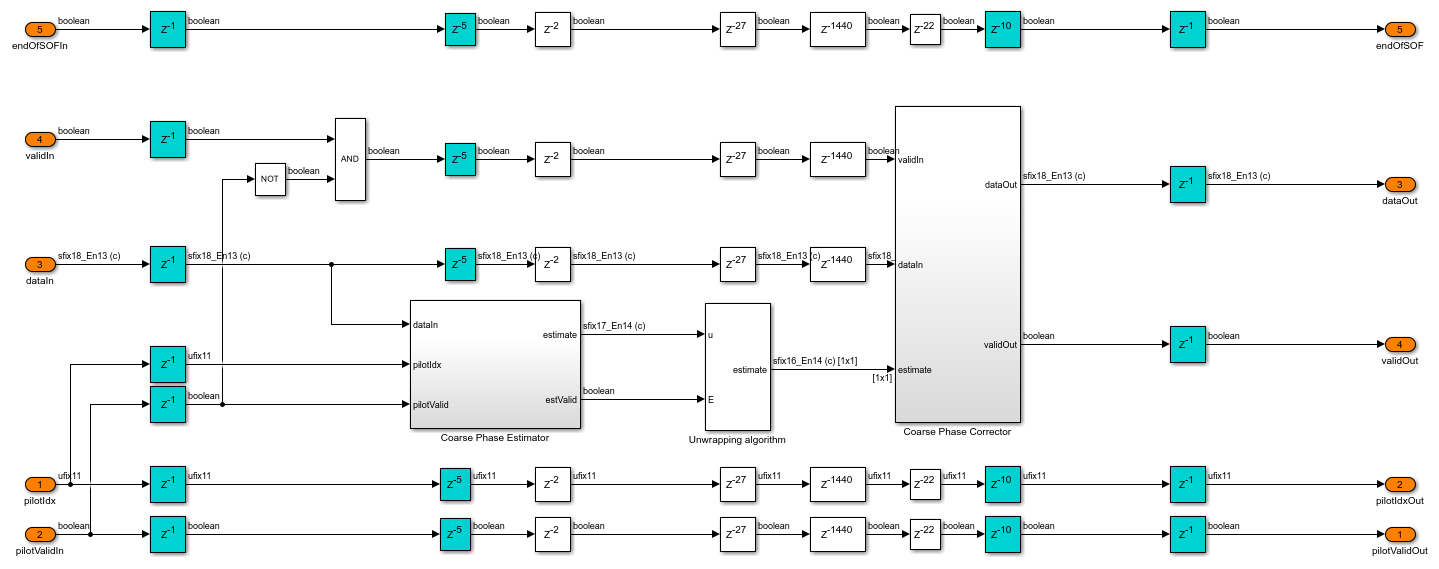

Coarse Phase Synchronizer

The Coarse Phase Synchronizer subsystem uses the pilot aided linear interpolation technique. The Coarse Phase Estimator subsystem estimates the complex phase from each of the 36 pilot symbols and performs averaging, which results in one estimate from each pilot block. The Unwrapping Algorithm subsystem implements the equation C.7 in section C.6.1 of [ 2 ] and interpolates the complex phase estimate from two consecutive pilot blocks. This interpolated estimate is used to compensate the phase of the symbols in between these two consecutive pilot blocks.

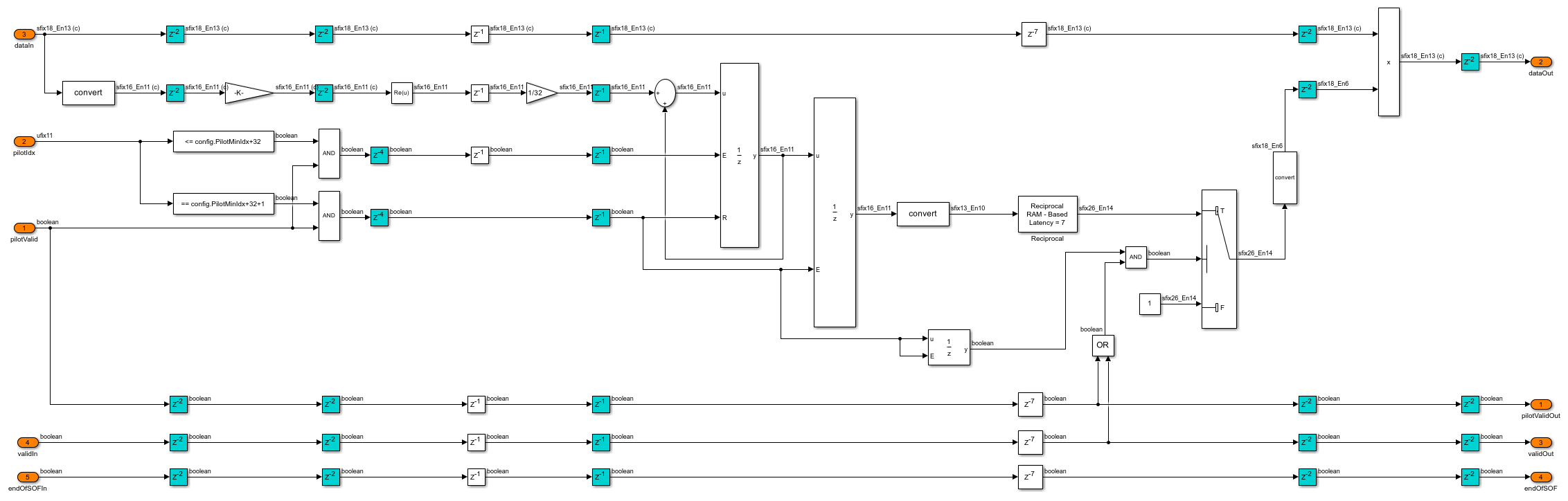

Fine Gain Control

The Fine Gain Control subsystem performs magnitude correction using the estimates derived from the pilot symbols. The input sequence is time and frequency synchronized before gain control. Each estimate is derived by multiplying the pilot symbol in the input sequence with reference pilot. The divide (1/32 gain block) and the integrator averages 32 estimates and stores in a register. The input is divided with the averaged estimate to correct the input magnitude.

Variance Estimator

The Variance Estimator subsystem computes the noise variance of the input signal. The input sequence is time and frequency synchronized and gain-corrected before estimating the variance. The reference pilot symbols are subtracted from the noise affected pilot symbols in the input sequence to generate zero-mean noisy symbols. The variance is computed by absolute squaring these symbols and averaging previous 2048 symbols using a moving average filter of length 2048.

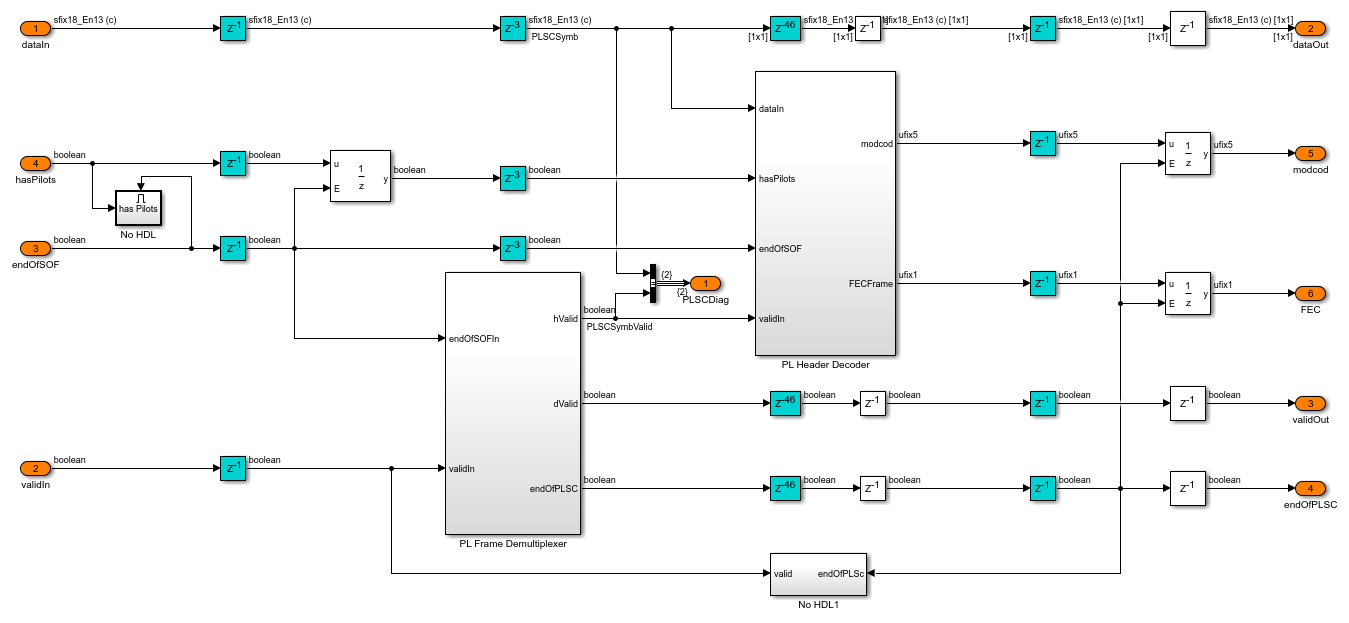

PL Header Recovery

The PL Header Decoder subsystem in the PL Header Recovery subsystem decodes the PLSC symbols of the PL header on a frame-by-frame basis to get the MODCOD and FECFrame type of a frame.

MODCOD indicates the modulation and coding scheme of the frame, and FECFrame indicates the type of the frame (short or normal) as described in sections 5.5.2.2 and 5.5.2.3 of [ 1 ].

The PLSC symbols contain seven information bits that are bi-orthogonally encoded with a (64,7) code. The construction of the 64 bit code is such that each odd bit in the code is either always a flipped bit or equal to the even consecutive bit based on whether the pilots exist or does not exist in the frame respectively, as described in section 5.5.2.4 of [ 1 ]. The 64 encoded bits are pi/2-BPSK modulated as described in section 5.5.2 of [ 1 ].

The PL Frame Demultiplexer subsystem demultiplexes the PLSC symbols and the PL data frame of the input. The signals from the hvalid and dvalid ports indicate the locations of PLSC symbols and PL data frame symbols respectively. The PLSC symbols are streamed into the PL Header Decoder subsystem.

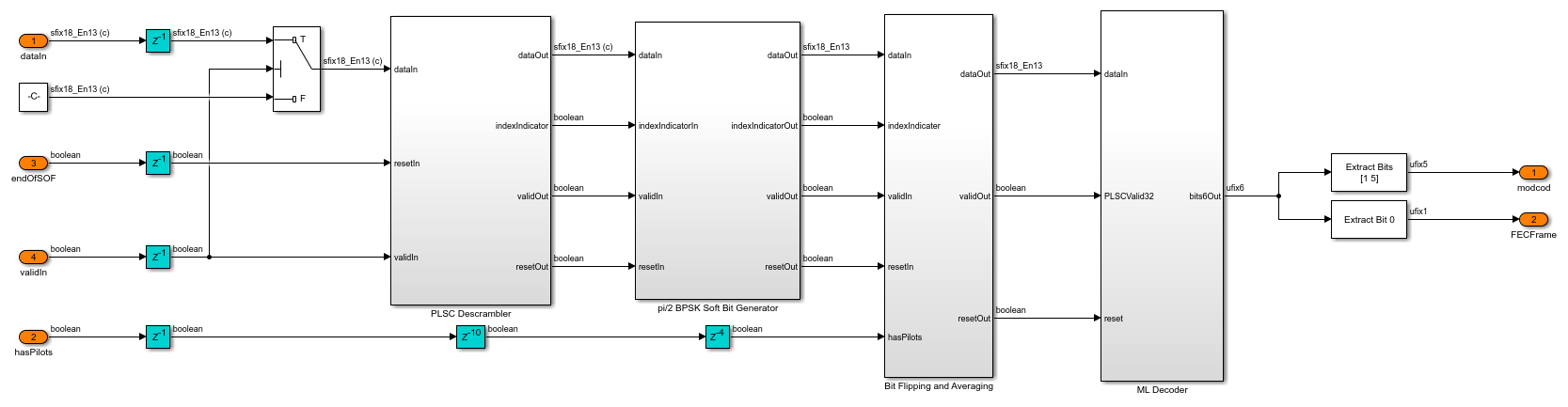

PL Header Decoder

The PLSC Descrambler subsystem in the PL Header Decoder subsystem descrambles the PLSC symbols. The signal from the indexIndicator port of the PLSC Descrambler subsystem distinguishes the even and odd locations of the PLSC symbols. The pi/2 BPSK Soft Bit Demodulator subsystem demodulates the PLSC symbols. If the pilots exists in the current PLFRAME (which is decided in the frame synchronization), the Bit Flipping and Averaging subsystem multiplies the odd soft bits by –1 in the PLSC symbols. A bit flip for a hard bit is same as multiplying by –1 for a soft bit. The subsystem averages the soft bits in even and odd locations to get one estimate. Likewise, 32 soft bits are generated from 64 soft bits. A maximum likelihood (ML) decoder is used to decode the (32,6) bi-orthogonal encoded bits. The 6 decoded bits are used to construct the MODCOD and FECFrame type.

ML Decoder

The ML Decoder subsystem decodes the (32,6) bi-orthogonal code by choosing the maximum likelihood codeword. A total of 2^6 = 64 codeword combinations, each 32 bits wide, are precomputed in the dvbs2hdlRxParameters.m file. The codewords are stored as integers in the uint32 format, with the first 32 codewords in one look-up table (LUT) and the next 32 codewords in another LUT. The LUT storing is such that the most significant bit of all of the codewords is called first, followed by the next significant bits, and so on. A bit level Euclidean distance is computed in the Compute Euclidean Distance subsystem with –1 and 1 as reference values for bit 0 and bit 1, respectively. The Euclidean Distance Sum Up subsystem adds all of the 32 bit level Euclidean metrics over time and generates a codeword Euclidean metric for each codeword. This subsystem uses a for each iterator to repeat the execution for all of the codewords and generates 64 codeword Euclidean metrics. The minimum Euclidean metric of 64 combinations maps to the maximum likelihood codeword. The maximum likelihood code word is used to construct the 6 bit input, and the MODCOD and FECFrame type values.

For a hardware-friendly implementation, the Euclidean metric is computed (computing involves multipliers) outside the ML Decoder subsystem as it uses a for each iterator.

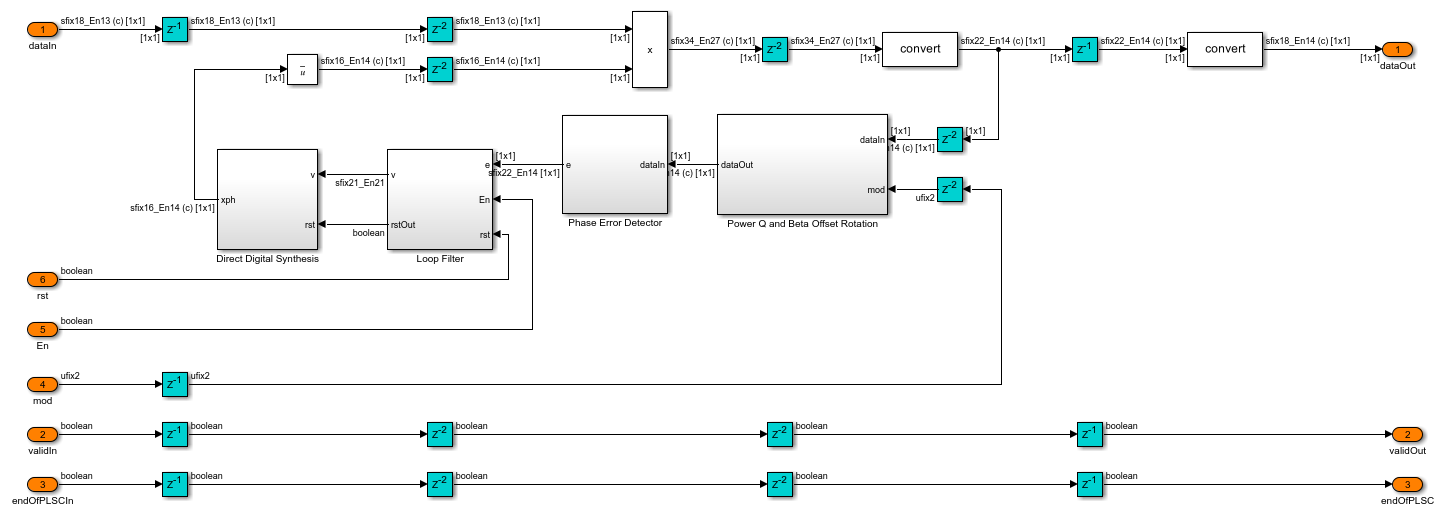

Fine Phase Synchronizer

The Fine Phase Synchronizer subsystem is a PLL implementation. Its normalized loop bandwidth is set to 20e-6. The MODCOD value decoded from the PL header specifies the modulation type of the symbols in the frame. The Power Q and Beta Offset Rotation subsystem raises the QPSK, 8-PSK, 16-APSK, and 32-APSK symbols to a power of Q and rotates the constellation by an angle of beta. The Phase Error Detector subsystem computes the phase error from the output of the Power Q and Beta Offset Rotation subsystem, as described by equation C.10 in annex C.6.2 of [ 2 ]. The phase error is filtered by the loop filter. The filtered output drives the NCO block in the Direct Digital Synthesis subsystem to generate the complex exponential sinusoidal samples, which are conjugated and used to correct the phase of the input samples. A reset signal rstCCFO resets the loop filter and restarts the estimation process.

This table shows the Q and beta values for the modulated symbols

Modulation Q Beta (in radians)

__________ _ _________________

QPSK 1 0

8-PSK 2 pi/4

16-APSK 3 0

32-APSK 4 pi/4

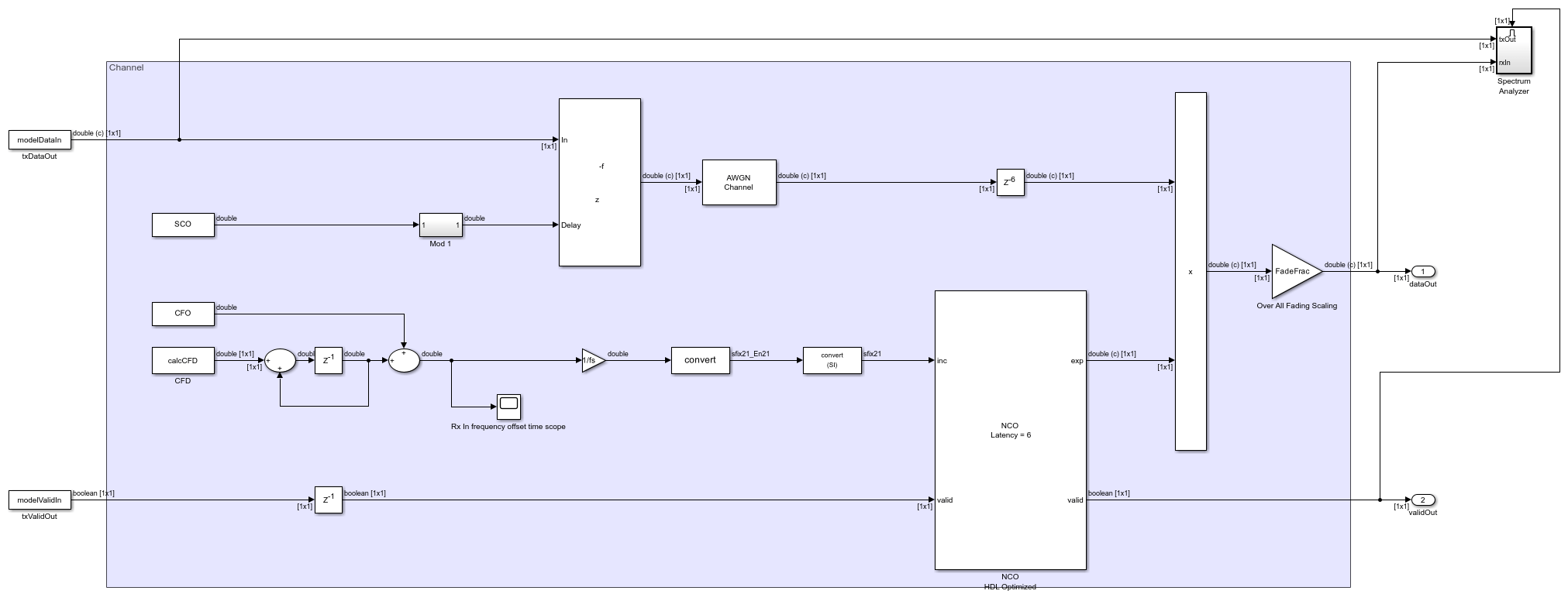

Channel

The Channel subsystem introduces the impairments in this table.

Impairment Description

____________________________________ ___________________________________

Fading Factor Specified in the interval [0.9,1.1]

Additive white Gaussian noise (AWGN) Specified in Es/N0 in dB

Carrier frequency offset (CFO) Specified in Hz

Carrier frequency drift (CFD) Specified in Hz/second

Carrier phase offset (CPO) Specified in degrees

Sampling clock offset (SCO) Specified in the interval [0,1)

Phase noise Specified as Low, Medium, High

This table defines the phase noise mask level in dBc/Hz that the phase noise generator in the dvbs2hdlPhaseNoise.m file uses to generate the phase noise and introduce in the transmitter output signal.

Frequency Low Medium High

_________ ____ ______ ____

100 Hz -73 -59 -25

1 KHz -83 -77 -50

10 KHz -93 -88 -73

100 KHz -112 -94 -85

1 MHz -128 -104 -103

Run the Model

Set the symbol rate, MODCOD, FECFrame type values, input stream format, user packet length and channel impairments on the Input Configuration subsystem mask and run the dvbs2hdlPLHeaderRecovery.slx model. Alternatively, to run the model, execute this command at the MATLAB command prompt.

sim dvbs2hdlPLHeaderRecovery

The MODCOD and FECFrame type values must be row vectors. Each element of the row vector corresponds to a frame.

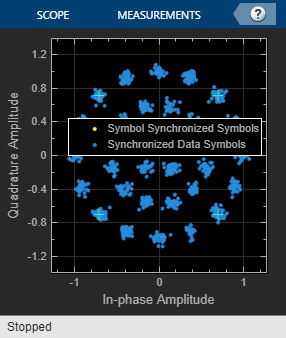

Verification and Results

Run the dvbs2hdlPLHeaderRecovery.slx model.

### Searching for referenced models in model 'dvbs2hdlPLHeaderRecovery'. ### Total of 1 models to build. ### Model reference simulation target for dvbs2hdlSyncPLHeaderRecoveryCore is up to date. Build Summary 0 of 1 models built (1 models already up to date) Build duration: 0h 0m 8.0048s Number of frames synced = 68 out of 68 Initial frames not compared = 39 Number of frames lost due to PL header mismatch = 0 out of 29 Number of frames lost due to BB header CRC failure = 0 out of 29 Number of packets errored = 0 out of 557 Number of bits errored = 0 out of 837728

HDL Code Generation

To generate the HDL code for this example, you must have HDL Coder™. Use makehdl and makehdltb commands to generate HDL code and HDL testbench for the Synchronization and PL Header Recovery subsystem. The testbench generation time depends on the simulation time.

The resulting HDL code is synthesized for a Xilinx® Zynq®-7000 ZC706 evaluation board. The post place and route resource utilization are shown in this table. The maximum frequency of operation is 201.5 MHz.

Resources Usage

_______________ _____

Slice LUT 46789

Slice Registers 64715

RAMB36 22

RAMB18 5

DSP48 252

References

ETSI Standard EN 302 307-1 V1.4.1(2014-11). Digital Video Broadcasting (DVB); Second Generation Framing Structure, Channel Coding and Modulation Systems for Broadcasting, Interactive Services, News Gathering and other Broadband Satellite Applications (DVB-S2).

ETSI Standard TR 102 376-1 V1.2.1(2015-11). Digital Video Broadcasting (DVB); Implementation Guidelines for the Second Generation System for Broadcasting, Interactive Services, News Gathering and other Broadband Satellite Applications (DVB-S2).

Marco Luise and Ruggero Reggiannini, Carrier Frequency Recovery in All-Digital Modems for Burst-Mode Transmissions.

Michael Rice, Digital Communications - A Discrete-Time Approach, Prentice Hall, April 2008.