Converting to Fixed Point | FPGA Design with MATLAB, Part 4

From the series: FPGA Design with MATLAB

Efficient hardware implementation requires quantizing your data types to fixed point. Signal-processing algorithms can be challenging to convert while maintaining required precision, especially if you are writing RTL by hand. The Model-Based Design approach lets you easily explore and visualize different options and automates much of the process. This part of the tutorial shows the basic concepts and the general approaches you can use.

This video covers:

- Converting default 64-bit double-precision data types to fixed-point representation

- Fixed-point data type definition in MATLAB® and Simulink® environments

- Propagation of data types to maintain precision during mathematical computations

- Model checks for consistency and precision to ensure predictable implementation results

- Comparison and verification of the fixed-point model design with golden reference

Published: 25 Sep 2019

Welcome to the HDL Coder Video Series. In this video series we will learn a popular production proven path to take a MATLAB digital signal-processing algorithm through Simulink, Fixed-Point Designer, and HDL Coder to target an FPGA.

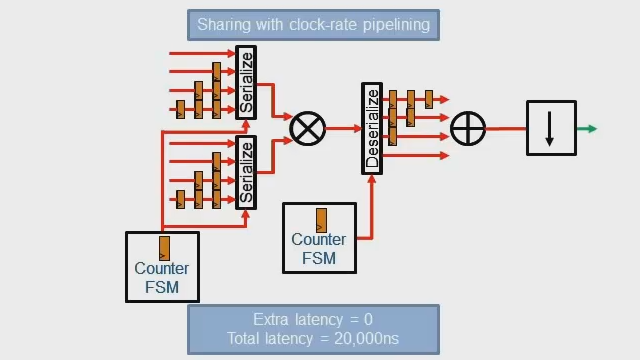

In previous videos in this series, we have discussed the strength of MATLAB and Simulink, created the Simulink model of the pulse detection algorithm, and introduced design architecture options that extend control over speed and area tradeoffs. In part four of the video series we will show how to convert the Simulink model to fixed-point data type and compare the Simulink fixed-point model to the MATLAB golden reference. Numbers in MATLAB and Simulink default to double precision floating-point data type, which is 64 bits. We will convert to fixed-point data types and operations to reduce hardware resources and computation steps.

In MathWorks, fixed-point data type is characterized by the word size in bits, the binary point, and whether it is signed or unsigned. The position of the binary point is how fixed-point values are scaled and interpreted. We will define our fixed-point specification in the test bench script and invoke them from the MATLAB workspace.

We will rename and save the model and utilize the data type conversion block to convert the workspace signal to fixed point. The DT_input specification ranges from -1 to 1, which is enough to represent the noisy receive signal. The Filter block is set to perform multiply and add using full-precision fixed-point data types when we set the “coefficients data type” on the filter block to DT_coeff.

Simulink automatically propagates fixed-point data types to maintain precision and visualizes it for you. It is recommended to maintain full precision until you get to a multiply, and then convert it down to 18 bits so that it maps to a single DSP slice on an FPGA. To visualize the filter output, run the test bench script Pulse_Detector_v3_tb. The resultant output from the filter block now has a word length of 40 and its fraction length is 37.

Running the test script during the initial stages of conversion to fixed point will cause errors, which we will ignore for the time being.

In the Compute Power subsystem, using the Data Type Conversion block at the input we will reduce the word length from 40 to 18 using the DT_filter specification and at the end stage of the adder, reduce the word length from 36 to 18 using the DT_power specification. Update the model at each of the data conversion step to see the change of the word lengths through the operations.

At the Local Peak subsystem, we will use a different method to inherit the data type by using the Data Type Duplicate block. Connect one port to the Threshold Constant block, whose output is set to “Inherit from back propagation” and another to the tapped delay block output.

In addition, we will change the detected value in the script of the MATLAB function block to true and false, respectively. With these changes completed, update the model and it should be error free. The error in previous stages was due to the data type mismatch between the threshold and tapped delay block signals.

When comparing the two signals in the MATLAB function block, Simulink requires the signals to be of the same type and size. Furthermore, the detected signal from the MATLAB function block which feeds into the Unit Delay Enabled block needs to be a Boolean data type. This is realized by changing to “true and false” Boolean format in the MATLAB function block script.

In this example we have been able to manually convert the data types. In complex designs, the Fixed-Point Designer runs simulations and collects the required ranges and precisions. From these simulations it proposes the fixed-point types which one can accept, adjust, apply, and run comparisons. This is all managed in workflow-oriented Graphical User Interface [GUI], where you can analyze and iterate quickly.

Also keep in mind, generating native floating point is a quick way to get started targeting hardware. It will use more resources but you can apply it to parts of your design that require a large dynamic range to overcome tricky quantization problems.

Using the test bench script pulse_detector_v3_tb, we compare the output of the MATLAB golden reference and the fixed-point Simulink model.

When converting from floating point to fixed point, we have introduced quantization errors. These errors occur due to scaling and saturation.

Hence, there is an increased error between the MATLAB golden reference output compared to the floating-point Simulink design. Quantization errors are expected—the whole process is a tradeoff between efficiency and accuracy.

In the fourth part of this video series on the HDL Coder, we have converted the Simulink model design to fixed-point data type. Additionally, we have showcased Simulink’s ability to visualize, propagate data, and validate the outcome is within a tolerance.

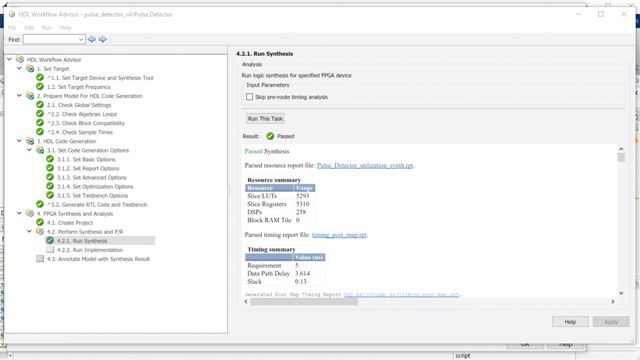

In the next video we will generate and synthesize the optimized HDL code.