General CRC Generator

Generate CRC code bits according to generator polynomial and append to input data frames

Libraries:

Communications Toolbox /

Error Detection and Correction /

CRC

Description

The General CRC Generator block generates cyclic redundancy check (CRC) code bits for each input data frame and appends them to the frame. For more information, see CRC Generator Operation.

Examples

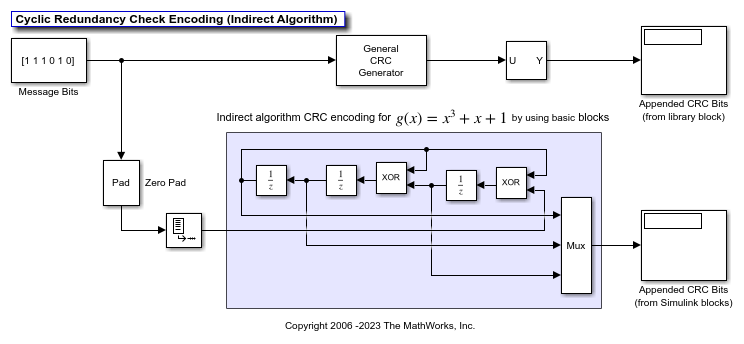

Configure a CRC with the g(x) = x³ + x + 1 generator polynomial and indirect algorithm to append CRC bits to a frame by using Simulink® blocks and compare the results to the operation of the General CRC Generator block in the Communications Toolbox™ with the same configuration.

The cm_crcgen_indirect model runs both CRC generators with the register set to a specific initial state and for a known 6 bit long input message. The initial states are loaded into the workspace variable iniStates by using the PreLoadFcn callback function. For more information, see Model Callbacks (Simulink).

Running the simulation displays the appended CRC bits that are generated by using the General CRC Generator block and the CRC generated by using a generator polynomial built by using Simulink® blocks. View the model output to confirm that the results of both implementations match. You can run the model with different message bits or with different initial states. To adjust the initial states, change the iniStates workspace variable before to running the simulation.

For other changes to the CRC generator, such as specifying a higher order polynomial, you must revise the layout of the model blocks for the polynomial generator that is built from individual Simulink® blocks. However, to reconfigure the General CRC Generator block, you can simply update its parameter settings.

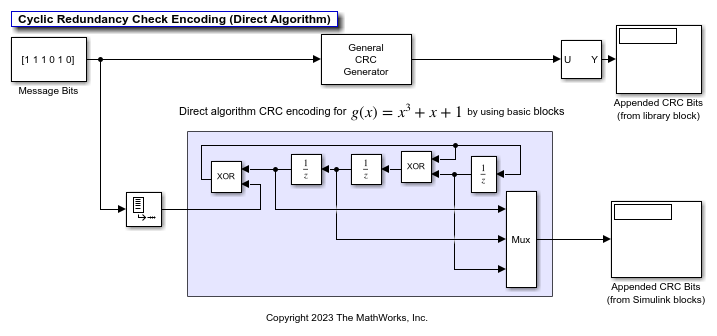

Configure a CRC with the g(x) = x³ + x + 1 generator polynomial and direct algorithm to append CRC bits to a frame by using Simulink® blocks and compare the results to the operation of the General CRC Generator block in the Communications Toolbox™ with the same configuration.

The cm_crcgen_direct model runs both CRC generators with the register set to a specific initial state and for a known 6 bit long input message. The initial states are loaded into the workspace variable iniStates by using the PreLoadFcn callback function. For more information, see Model Callbacks (Simulink).

Running the simulation displays the appended CRC bits that are generated by using the General CRC Generator block and the CRC generated by using a generator polynomial built by using Simulink® blocks. View the model output to confirm that the results of both implementations match. You can run the model with different message bits or with different initial states. To adjust the initial states, change the iniStates workspace variable before to running the simulation.

For other changes to the CRC generator, such as specifying a higher order polynomial, you must revise the layout of the model blocks for the polynomial generator that is built from individual Simulink® blocks. However, to reconfigure the General CRC Generator block, you can simply update its parameter settings.

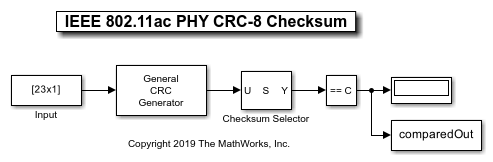

Generate a CRC-8 checksum for the example shown in 802.11™-2016, section 21.3.10.3 and compare with the expected CRC.

Explore the Model

To align with the CRC calculation in 802.11-2016, the General CRC Generator block mask sets the generator polynomial to  , initial states to 1, final XOR parameter to 1, and selects direct method.

, initial states to 1, final XOR parameter to 1, and selects direct method.

The simulation is configured to process one input frame modeling the example from the 802.11-2016 standard in section 21.3.10.3. In the example, the input bit stream {m0, … m22} is {1 0 0 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1} and the expected CRC checksum {c7, … c0} is {0 0 0 1 1 1 0 0}. The generated CRC checksum bits are compared to the expected bits and a 1 is output for each equal bit in the 8 bit CRC checksum.

comparedOut = 8×1 logical array 1 1 1 1 1 1 1 1

References

[1] IEEE Std 802.11™-2016 IEEE Standard for Information Technology—Local and Metropolitan Area Networks—Specific Requirements Part 11: Wireless LAN MAC and PHY Specifications.

Ports

Input

Input signal, specified as a binary column vector. The length of the input frame must be a multiple of the value of the Checksums per frame parameter.

Data Types: double | Boolean

Output

Output codeword frame, returned as a binary column vector that inherits the data type of the input signal. The output contains the input data frames with the CRC bit sequences appended to them.

The length of the output frame is m + k * r, where m is the size of the input frame, k is the number of checksums per frame, and r is the degree of the generator polynomial.

Parameters

To edit block parameters interactively, use the Property Inspector. From the Simulink® Toolstrip, on the Simulation tab, in the Prepare gallery, select Property Inspector.

Generator polynomial for the CRC algorithm, specified as one of the following:

A polynomial character vector such as

'z^3 + z^2 + 1'.A binary row vector that represents the coefficients of the generator polynomial in order of descending power. The length of this vector is (N+1), where N is the degree of the generator polynomial. For example,

[1 1 0 1]represents the polynomial x3+ z2+ 1.An integer row vector containing the exponents of z for the nonzero terms in the polynomial in descending order. For example,

[3 2 0]represents the polynomial z3 + z2 + 1.

For more information, see Representation of Polynomials in Communications Toolbox.

The default value is the CRC-16-CCITT generator polynomial. This table lists some commonly used generator polynomials.

| CRC Name | Generator Polynomial |

|---|---|

| CRC-32 | 'z^32 + z^26 + z^23 + z^22 + z^16 + z^12 + z^11 + z^10 + z^8 +

z^7 + z^5 + z^4 + z^2 + z + 1' |

| CRC-24 | 'z^24 + z^23 + z^14 + z^12 + z^8 + 1' |

| CRC-16 | 'z^16 + z^15 + z^2 + 1' |

| CRC-16-CCITT | 'z^16 + z^12 + z^5 + 1' |

| Reversed CRC-16 | 'z^16 + z^14 + z + 1' |

| CRC-8 | 'z^8 + z^7 + z^6 + z^4 + z^2 + 1' |

| CRC-4 | 'z^4 + z^3 + z^2 + z + 1' |

Example: 'z^7 + z^2 + 1', [1 0 0 0 0 1 0

1], and [7 2 0] represent the same

polynomial, p(z) =

z

7 + z

2 + 1.

Initial states of the internal shift register, specified as a binary scalar or a binary row vector with a length equal to the degree of the generator polynomial. A scalar value is expanded to a row vector of equal length to the degree of the generator polynomial.

Select to use the direct algorithm for CRC checksum calculations. When cleared, the block uses the non-direct algorithm for CRC checksum calculations.

For more information on direct and non-direct algorithms, see Error Detection and Correction.

Select to flip the input data on a bytewise basis before entering the data

into the shift register. When Reflect input bytes is

selected, the input frame length divided by the value of the Checksums per frame parameter must be an

integer and a multiple of 8. When Reflect input

bytes is cleared, the block does not flip the input

data.

Select to flip the CRC checksums around their centers after the input data are completely through the shift register. When Reflect checksums before final XOR is cleared, the block does not flip the CRC checksums.

Final XOR, specified as a binary scalar or a binary row vector with a

length equal to the degree of the generator polynomial. The XOR operation

runs using the value of the Final XOR parameter the CRC

checksum before appending the CRC to the input data. A scalar value is

expanded to a row vector of equal length to the degree of the generator

polynomial. A setting of 0 is equivalent to no XOR

operation.

Number of checksums calculated for each frame, specified as a positive integer.

Block Characteristics

Data Types |

|

Multidimensional Signals |

|

Variable-Size Signals |

|

Algorithms

The General CRC Generator block supports generation of CRC checksum by using the indirect or direct CRC algorithm.

Indirect CRC Algorithm

The indirect CRC algorithm accepts a binary data vector, corresponding to a polynomial M, and appends a checksum of r bits, corresponding to a polynomial C. The concatenation of the input vector and the checksum then corresponds to the polynomial T = M×xr + C, since multiplying by xr corresponds to shifting the input vector r bits to the left. The algorithm chooses the checksum C so that T is divisible by a predefined polynomial P of degree r, called the generator polynomial.

The algorithm divides T by P, and sets the checksum equal to the binary vector corresponding to the remainder. That is, if T = Q×P + R, where R is a polynomial of degree less than r, the checksum is the binary vector corresponding to R. If necessary, the algorithm prepends zeros to the checksum so that it has length r.

The CRC generation feature, which implements the transmission phase of the CRC algorithm, does the following:

Left shifts the input data vector by r bits and divides the corresponding polynomial by P.

Sets the checksum equal to the binary vector of length r, corresponding to the remainder from step 1.

Appends the checksum to the input data vector. The result is the output vector.

The CRC detection feature computes the checksum for its entire input vector, as described above.

The CRC algorithm uses binary vectors to represent binary polynomials, in descending order of powers. For example, the vector [1 1 0 1] represents the polynomial x3 + x2 + 1.

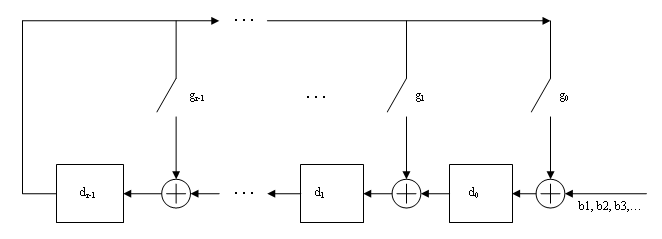

Bits enter the linear feedback shift register (LFSR) from the lowest index bit to the highest index bit. The sequence of input message bits represents the coefficients of a message polynomial in order of decreasing powers. The message vector is augmented with r zeros to flush out the LFSR, where r is the degree of the generator polynomial. If the output from the leftmost register stage d(1) is a 1, then the bits in the shift register are XORed with the coefficients of the generator polynomial. When the augmented message sequence is completely sent through the LFSR, the register contains the checksum [d(1) d(2) . . . d(r)]. This is an implementation of binary long division, in which the message sequence is the divisor (numerator) and the polynomial is the dividend (denominator). The CRC checksum is the remainder of the division operation.

Direct CRC Algorithm

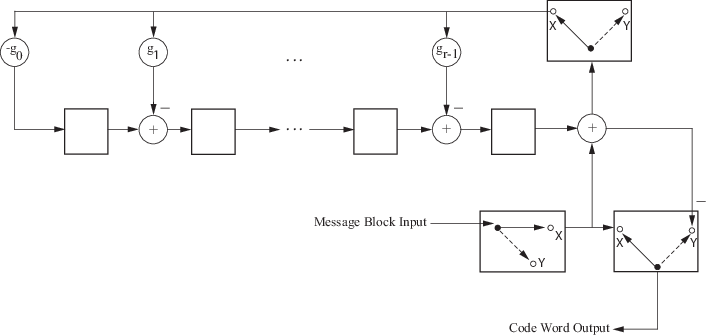

This block diagram shows the direct CRC algorithm.

Where Message Block Input is and Code Word Output is

The initial step of the direct CRC encoding occurs with the three switches in position X. The algorithm feeds k message bits to the encoder. These bits are the first k bits of the code word output. Simultaneously, the algorithm sends k bits to the linear feedback shift register (LFSR). When the system completely feeds the kth message bit to the LFSR, the switches move to position Y. Here, the LFSR contains the mathematical remainder from the polynomial division. These bits are shifted out of the LFSR and they are the remaining bits (checksum) of the code word output.

The CRC generator appends CRC checksums to the input frame according to the specified generator polynomial and number of checksums per frame.

For a specific initial state of the internal shift register and k checksums per input frame:

The input signal is divided into k subframes of equal size.

Each of the k subframes are prefixed with the initial states vector.

The CRC algorithm is applied to each subframe.

The resulting checksums are appended to the end of each subframe.

The subframes are concatenated and output as a column vector.

For the scenario shown here, a 10-bit frame is input, a z3 + z2 + 1 generator polynomial computes the CRC checksum, the initial state is 0, and the number of checksums per frame is 2.

The input frame is divided into two subframes of size 5, and checksums of size 3 are computed

and appended to each subframe. The initial states are not shown because an initial state of

[0] does not affect the output of the CRC algorithm. The output

transmitted codeword frame has the size 5 + 3 + 5 + 3 = 16 bits.

References

[1] Sklar, Bernard. Digital Communications: Fundamentals and Applications. Englewood Cliffs, N.J.: Prentice-Hall, 1988.

[2] Wicker, Stephen B. Error Control Systems for Digital Communication and Storage. Upper Saddle River, N.J.: Prentice Hall, 1995.

Extended Capabilities

C/C++ Code Generation

Generate C and C++ code using Simulink® Coder™.

Version History

Introduced before R2006a

See Also

Functions

Blocks

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

选择网站

选择网站以获取翻译的可用内容,以及查看当地活动和优惠。根据您的位置,我们建议您选择:。

您也可以从以下列表中选择网站:

如何获得最佳网站性能

选择中国网站(中文或英文)以获得最佳网站性能。其他 MathWorks 国家/地区网站并未针对您所在位置的访问进行优化。

美洲

- América Latina (Español)

- Canada (English)

- United States (English)

欧洲

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)