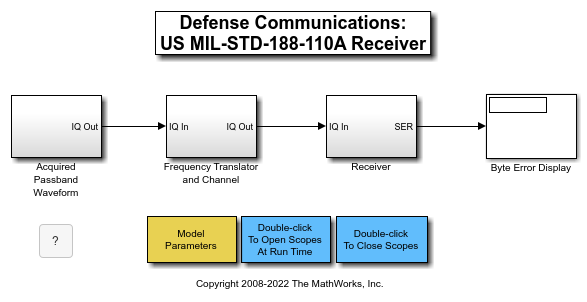

Defense Communications: US MIL-STD-188-110A Receiver

This model shows a communications system compliant with the U. S. MIL-STD-188-110A military standard. In particular, the model implements a full receiver that demodulates and outputs a text message, which was modulated by a reference transmitter and captured with data acquisition equipment. This model supports a 1200 bps data rate. It also implements an interleaver length of 0.6 s.

The system described in this standard is intended for long-haul and tactical communications over HF (high frequency) channels. The system is compatible with the NATO standard STANAG 4539.

Structure of the Example

This example consists of the following pieces, further described in the sections below:

Acquired Passband Waveform - Outputs a bandpass MIL-STD-188-110A waveform centered at 1800 Hz

Frequency Translator and Channel - Downconverts the signal to complex baseband and processes it with a choice of channels

Receiver - Performs synchronization and baseband processing, and outputs a text message

Acquired Passband Waveform

The Acquired Passband Waveform subsystem uses a MATLAB® workspace variable to stream as an output. This variable represents data that has been generated by a standard-compliant transmitter and captured with data acquisition equipment. The nominal sample rate of the A/D is 9600 sps, but the actual A/D sampling rate is somewhat offset from that value, resulting in a symbol timing frequency offset.

Frequency Translator and Channel

This subsystem performs ideal downconversion to complex baseband, then processes the input signal with a choice of four successively degraded channels:

a noiseless channel

an AWGN channel

a static frequency selective channel plus AWGN

a fading frequency selective channel plus AWGN

The fading frequency selective channel is implemented by the SISO Fading Channel library block.

The use of multiple channels allows you to investigate their effects on receiver performance, especially that of the symbol synchronization blocks. The noiseless channel most effectively isolates the operation of the receiver, and the AWGN-only and static frequency selective channels show a graceful degradation in performance. The fading frequency selective channel models the moderate Watterson channel described in [2].

Receiver

The MIL-STD-188-110A receiver consists of four subsystems:

RRC Filter and AGC

Preamble Detect to Enable Downstream Processing

Carrier Recovery, Timing Recovery, and Equalization

Demodulation and Error Correction

The RRC Filter and AGC subsystem performs square root raised cosine filtering on the received signal, providing matched filtering for the transmitted waveform. The AGC ensures that the average signal power into the equalizer is 1 watt. This operation ensures that the constellation of the equalizer input signal is most closely matched to the ideal constellation against which it makes symbol decisions.

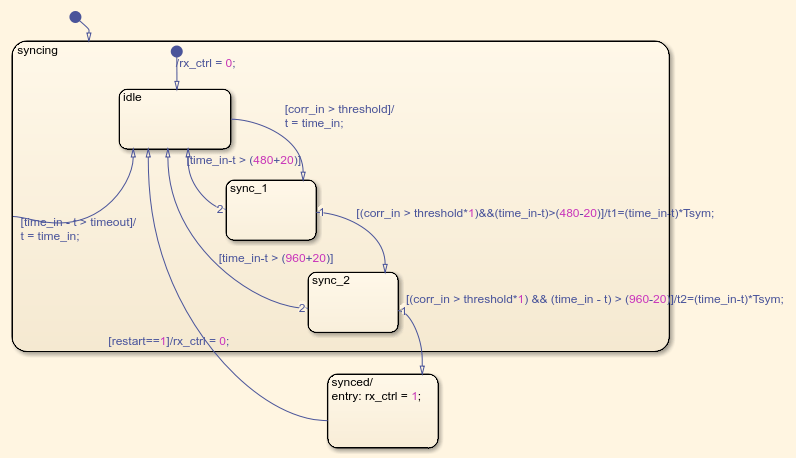

The Preamble Detect to Enable Downstream Processing subsystem performs a correlation on the known 0.6 sec synchronization preamble, which consists of three virtually identical 0.2 sec data segments. It detects three consecutive correlation peaks at 0.2, 0.4, and 0.6 sec in order to declare preamble detection. Once the preamble is detected, the subsystem sends a control signal to turn on the downstream processing, including: carrier recovery, timing recovery, equalization, demodulation, and error correction. The three consecutive peaks are detected with the Stateflow® state machine shown below. The block diagram shows the state machine in context with the preamble correlator, and the state machine is below the block diagram.

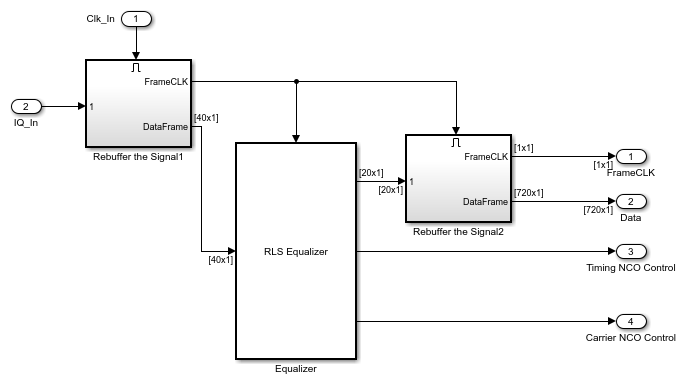

The Carrier Recovery, Timing Recovery, and Equalization subsystem uses a switchable NCO to generate a compensating sinusoid to remove the relatively constant carrier frequency offset. The NCO control signal is generated by estimating the phase error between the output of the RLS equalizer and its input. The RLS equalizer is implemented by the Decision Feedback Equalizer library block. The estimation is performed by computing the cross-spectrum between the equalizer input and its output, and performing a linear least squares fit on the resulting phase characteristic. The phase error is then filtered by a proportional-integral (PI) controller and fed to the carrier recovery NCO.

To compensate for the timing frequency error inherent in the acquired waveform, the Carrier Recovery, Timing Recovery, and Equalization subsystem uses a switchable timing control unit to generate a fractional delay value and a symbol clock. The fractional delay value is used to drive a variable delay block that uses a Farrow filter structure to interpolate its input. The variable delay is implemented by the Variable Fractional Delay library block.

The symbol clock, which runs at 9600 sps, is used to downsample the input signal, which is oversampled by four, down to the symbol rate of 2400 sym/sec. The clock typically goes high every four samples, but because of the timing frequency offset, it periodically goes high every five samples. The clock drives a rebuffering operation that creates symbol-spaced data in frames 40 samples long. These frames are ideally suited for processing by the RLS equalizer, since it has 40 taps. The rebuffering occurs in the Carrier Recovery, Timing Recovery, and Equalization -> Equalize and Re-Buffer subsystem. This subsystem also generates a frame clock that enables the RLS equalizer. This frame clock also runs at the oversampled rate of 9600 sps, but goes high nominally every 160 samples. Because of the timing frequency offset, it periodically goes high every 161 samples.

The pattern of using a high rate clock to drive a lower rate processing system can be used liberally in communications receiver designs. This pattern is shown in a more fundamental form in the DSP System Toolbox™ example WWV Digital Receiver - Synchronization and Detection. The Carrier Recovery, Timing Recovery, and Equalization -> Equalize and Re-Buffer subsystem is shown below:

The time delay incurred by the RLS equalizer is estimated once again by a cross-spectral technique, and is used to drive the NCO of the timing control unit. A linear least squares fit is made to the phase characteristic of the cross spectrum between the equalizer input and its output. The slope of this phase estimates the delay induced by the equalizer.

The Decision Feedback Equalizer block is configured to use the RLS algorithm' and has 20 feedforward and 20 feedback taps. A DFE structure is necessary because of the deep spectral nulls induced by the Watterson channel. The quickly converging RLS weight update algorithm is needed to combat the rapid fading of the Watterson channel. Half the data that the equalizer processes is training data. This large percentage of training data is necessary because of the rapidly fluctuating HF channel. Once the training data is discarded, the equalizer output rate is nominally 1200 sps. Also, the equalizer subsystem performs descrambling to undo the scrambling performed by the transmitter.

The Equalize and Re-Buffer subsystem also generates a frame clock to enable the downstream processing performed in the Demodulation and Error Correction subsystem. The data into that downstream subsystem is packaged in frames of 720 samples long, which corresponds to a time duration of 0.6 sec. This second frame clock, as with the first one, also runs at the oversampled rate of 9600 sps, but goes high nominally every 5760 samples. However, due to the previous downsampling by four to derive symbol-rate data, and the effective downsampling by two from discarding equalizer training data, the clock triggers roughly every 5760 / 8 = 720 samples. However, because of the timing frequency offset, the clock actually goes high either every 5762 or every 5763 samples.

The Demodulation and Error Correction subsystem performs the following functions:

Symbol extraction via QPSK demodulation

Modified Gray encoding

Block deinterleaving

Viterbi decoding of the rate 1/2, constraint length 7 convolutional code

Byte error rate calculations

End-of-message detection

Printing of the text message that drove the transmitter

Results and Displays

When you run the simulation, it displays these numerical or graphical results:

The byte error rate

The power spectrum of the channel output

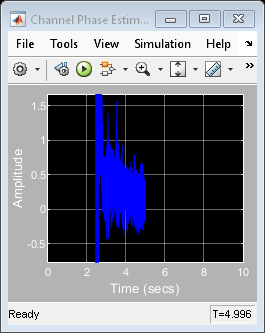

The estimate of the cross-spectral phase between the equalizer input and its output

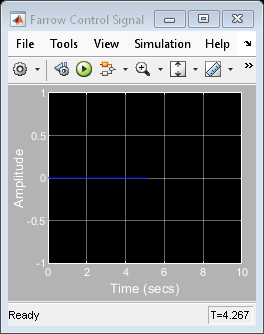

The control signal used to drive the Farrow fractional delay

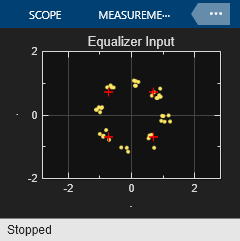

A scatter plot of the equalizer input

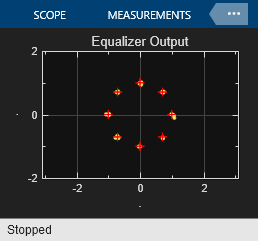

A scatter plot of the equalizer output

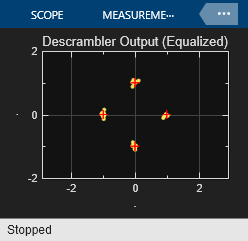

A scatter plot of the descrambler output

A window showing the demodulated, decoded text message

These plots are shown below, starting with the channel output power spectrum.

Below is the estimate of the cross-spectral phase between the equalizer input and its output.

Below is the control signal used to drive the Farrow fractional delay.

Below is the scatter plot of the equalizer input.

Below is the scatter plot of the equalizer output.

Below is the scatter plot of the descrambler output. Note that the 8PSK constellation has been collapsed to a QPSK constellation, per the MIL-STD-188-110A spec for this data rate.

Below is an excerpt from the demodulated message, which is taken from the MIL-STD-188-110a standard [1].

Exploring the Example

The example allows you to experiment with multiple system capabilities to examine their effect on byte error rate performance. For instance, you can view the effect of changing the channel model on the various displays. In particular, when you select the fading frequency selective channel, the channel phase estimate, the Farrow control signal, and the scatter plot displays are all noticeably degraded.

You can also enable or disable the timing control unit and the Farrow fractional delay. When the timing control unit is disabled, the demodulation operates properly for a time, but eventually the symbol timing frequency offset exceeds the length of the equalizer, which can no longer compensate for the delay. At that point, the demodulation process breaks down completely. When the Farrow fractional delay is disabled, and the timing control unit is enabled, the effect is more nuanced. However, in that case you can see the scatter plots flicker when the symbol timing crosses a symbol boundary. This is most easily seen in the noiseless case.

Take note of the quality of the demodulated message in the MATLAB figure window. For successively degraded channel and/or receiver configurations, the demodulated message becomes progressively more unreadable.

To generate executable code for this model, you will need to disable the display of the text message, via the Model Parameters subsystem. The block that performs the text printing is implemented with the Interpreted MATLAB Function block, which does not generate code.

Selected Bibliography

[1] MIL-STD-188-110B: Interoperability and Performance Standards for Data Modems, U. S. Department of Defense, 2000. (A superset of the MIL-STD-188-110A standard)

[2] ITU-R Recommendation 520-2: Use of High Frequency Ionospheric Channel Simulators, 1978/1982/1992.

See Also

The Defense Communications: US MIL-STD-188-110B Baseband End-to-End Link example shows both a MIL-STD-188-110B transmitter and receiver, without the synchronization operations. It also enables a flexible choice of data rates, whereas this example has a fixed data rate of 1200 bps.