Multiple Frame Support

Deep Learning HDL Toolbox™ supports multiple frame mode enabling you to write multiple images into the double data rate (DDR) memory and read back multiple results at the same time. To improve the performance of your deployed deep learning networks, use multiple frame mode.

Input DDR Format

To format input images to meet the multiple frame input DDR format, you must have:

The start address of the input data for the DDR

The DDR offset for a single input image frame

This information is automatically generated by the compile method.

For more information on the generated DDR address offsets, see Use the Compiler Output for System Integration.

You can also specify the maximum number of input frames as an optional argument in the

compile method.

For more information, see Generate DDR Memory Offsets Based on Number of Input Frames.

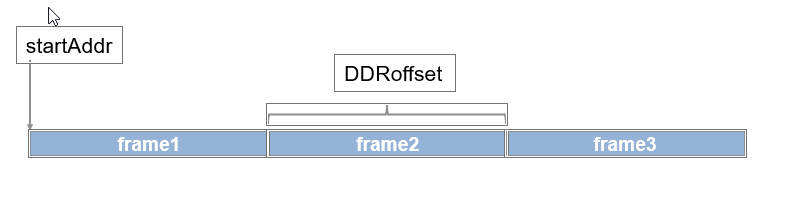

This graphic shows the format of the input area of the DDR for multiple input images.

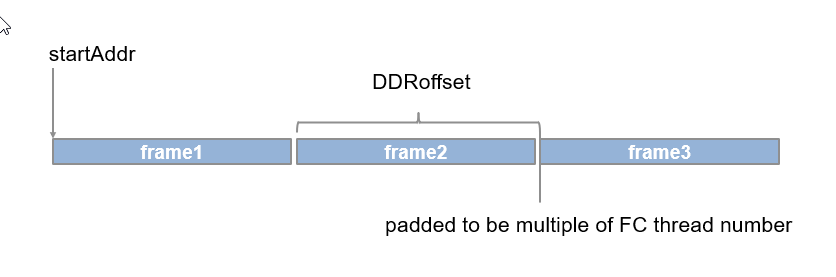

Output DDR Format

To retrieve the results for multiple image inputs from the output area of the DDR, you must have:

The start address of the output area of the DDR

The DDR offset of a single result

The output results must be formatted as a multiple of the FC output feature size. The

information and formatting are generated by the compile method.

For more information on the generated DDR address offsets, see External Memory Address Map.

This graphic shows the formatting of the output area of the DDR memory.

Manually Enable Multiple Frame Mode

After the deep learning network has been deployed, you can manually enable the multiple frame mode by writing the number of frames through a network configuration (NC) port. To manually enter the multiple frame mode at the MATLAB® command line enter:

dnnfpga.hwutils.writeSignal(1, dnnfpga.hwutils.numTo8Hex(addrMap('FrameCount')),15,hT);addrMap('FrameCount') returns the AXI register address for

FrameCount, 15 is the number of images, and hT represents the dlhdl.Target class

that contains the board definition and board interface definition. For more information

about the AXI register addresses, see Deep Learning Processor IP Core Report.

See Also

dlhdl.Target | dlhdl.Workflow | compile