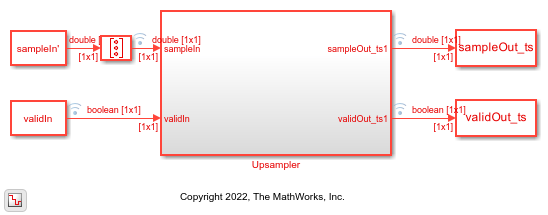

Upsampler

Libraries:

DSP HDL Toolbox /

Signal Operations

Description

The Upsampler block upsamples an input signal by adding L–1 zeros between input samples, where L is the upsampling factor. The block supports these combinations of input and output data.

Scalar input and scalar output

Scalar input and vector output

Vector input and vector output

The block provides an architecture suitable for HDL code generation and hardware deployment.

Note

You can also generate HDL code for this hardware-optimized algorithm, without creating a Simulink® model, by using the DSP HDL IP Designer app. The app provides the same interface and configuration options as the Simulink block.

Examples

Ports

Input

Input data, specified as a scalar or a column vector with a length up to 64. The input data must be an integer or a fixed-point value with a word length less than or equal to 128.

The block has an output ready signal that indicates when the block is ready to process new input data. Your design can react to the ready signal to provide the next input sample, or you can space your input data with enough cycles in between that the block can process each sample. For more information, see Backpressure Signal.

The double and

single data types are supported for simulation, but not for HDL

code generation.

Data Types: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | fixed point

Control signal that indicates whether the input data is valid. When this value is

1, the block accepts the values on the data

input port. When this value is 0, the block ignores the values on

the data input port.

Data Types: Boolean

Control signal that clears the internal states. When this value is

1, the block stops the current calculation and clears its

internal states. When this value is 0 and

valid is 1, the block captures data for

processing.

For more reset considerations, see the Reset Signal section on the Hardware Control Signals page.

Dependencies

To enable this port, on the Control Ports tab, select the Enable reset input port parameter.

Data Types: Boolean

Output

Upsampled data, returned as a scalar or a column vector with a length up to 1 to 128.

Data Types: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | fixed point

Control signal that indicates whether data from the data

output port is valid. When this value is 1, the block returns valid

data on the data output port. When this value is

0, the values on the data output port are

not valid.

Data Types: Boolean

Control signal that indicates whether the block can accept new input data. The

block sets this output to 1 (true) when it can

accept data, and to 0 (false) when it is

processing and cannot accept more data. For more information, see Backpressure Signal.

Dependencies

To enable this port, on the Control Ports tab, select the Enable ready output port parameter.

Data Types: Boolean

Parameters

Note

These parameters apply when configuring a block in Simulink or an algorithm in the DSP HDL IP Designer app.

Main

Specify the upsampling factor by which the block increases the input sampling rate.

Specify the sample offset as an integer in the range [0, Upsample factor (L) – 1].

Specify the minimum number of cycles between the valid input samples as a factor or multiple of Upsample factor (L) or an integer in the range [1, Inf] based on the type of input and output data.

| Input Data | Output Data | Minimum Number of Cycles Between Valid Input Samples |

|---|---|---|

| Scalar | Scalar | Greater than or equal to Upsample factor (L) |

| Scalar | Vector | Factor of Upsample factor (L) |

| Vector | Vector | Integer in the range [1, Inf] |

Control Ports

Select this parameter to enable the reset input port. The reset signal implements a local synchronous reset of the data path registers.

For more reset considerations, see Tips.

Select this parameter to enable the ready output port.

Algorithms

The latency of the block changes according to the length of the input. The latency of

the block is 1 when you set the Upsample factor (L) parameter to

1. This table shows the latency of the block.

| Input Data | Output Data | Latency in Clock Cycles |

|---|---|---|

| Scalar | Scalar | 3 |

| Scalar | Vector | 3 |

| Vector | Vector | 2 |

This figure shows the output of the block with the default configuration, when you set

the Upsample factor (L) and Sample offset (0 to

L-1) parameters to 3 and 0,

respectively. The latency of the block for a scalar input is three clock cycles.

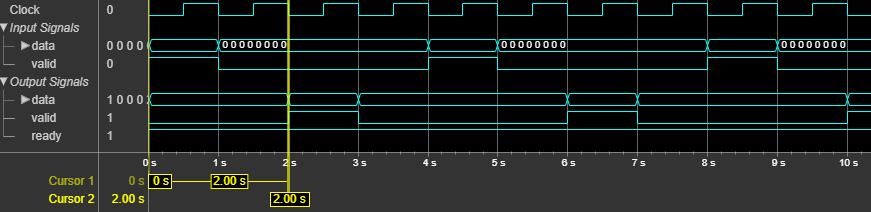

This figure shows the output of the block when you set the Upsample factor

(L) parameter value to 8 and the Sample offset

(0 to L-1) parameter to 1. The latency of the block is

three clock cycles.

This figure shows the output of the block for a two-element column vector input when

you set the Upsample factor (L) and Sample offset (0 to

L-1) parameters to 3 and 0,

respectively. The latency of the block is two clock cycles.

This figure shows the output of the block for an eight-element column vector input

when you set the Upsample factor (L) and Sample offset (0

to L-1) parameters to 4 and 0,

respectively. The latency of the block is two clock cycles.

The performance of the synthesized HDL code varies with your target and synthesis options. The performance also varies based on the input data type.

This table shows the resource and performance data synthesis results of the block for a

scalar input and for a 16-element column vector input of type

fixdt(1,16,0) when you set the Upsample factor (L)

and Sample offset (0 to L-1) parameters to 8 and

0, respectively. The generated HDL targets the AMD®

Zynq®- 7000 ZC706 Evaluation Board.

| Input Data | Slice LUTs | Slice Registers | Maximum Frequency in MHz |

|---|---|---|---|

| Scalar | 35 | 60 | 900.81 |

| Vector | 384 | 514 | 926.29 |

The resources and frequencies vary based on the type of input data and the value of Upsample factor (L), as well as other parameter values you select in the block mask. Using a vector input can increase the throughput, however, doing so also increases the number of hardware resources that the block uses.

Extended Capabilities

This block supports C/C++ code generation for Simulink accelerator and rapid accelerator modes and for DPI component generation.

HDL Coder™ provides additional configuration options that affect HDL implementation and synthesized logic.

This block has one default HDL architecture.

| ConstrainedOutputPipeline | Number of registers to place at

the outputs by moving existing delays within your design. Distributed

pipelining does not redistribute these registers. The default is

|

| InputPipeline | Number of input pipeline stages

to insert in the generated code. Distributed pipelining and constrained

output pipelining can move these registers. The default is

|

| OutputPipeline | Number of output pipeline stages

to insert in the generated code. Distributed pipelining and constrained

output pipelining can move these registers. The default is

|

| SynthesisAttributes |

Specifies the synthesis attributes for the blocks and block output signals in the model. The generated HDL code contains these attributes. For more information, see SynthesisAttributes (HDL Coder). |

Version History

Introduced in R2022b

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

选择网站

选择网站以获取翻译的可用内容,以及查看当地活动和优惠。根据您的位置,我们建议您选择:。

您也可以从以下列表中选择网站:

如何获得最佳网站性能

选择中国网站(中文或英文)以获得最佳网站性能。其他 MathWorks 国家/地区网站并未针对您所在位置的访问进行优化。

美洲

- América Latina (Español)

- Canada (English)

- United States (English)

欧洲

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)