Top-Level Models Using TriCores of Infineon AURIX

The TC39x series of Infineon®

AURIX™ microcontrollers comprises of six TriCores

(TriCore0 to TriCore5), TC38x

series has four TriCores (TriCore0 to

TriCore3), and the TC37x series has three TriCores

(TriCore0 to TriCore2). The

TriCore0 is the principal core and the remaining cores act as

auxiliary cores. You can create top-level models with referenced models using TriCore

processing units to implement different application models.

Every participating core of the multicore model must have information about other participating cores of the application model. For example, consider a top-model with three referenced models using the TriCore 0, TriCore 1, and TriCore 2 processing units.

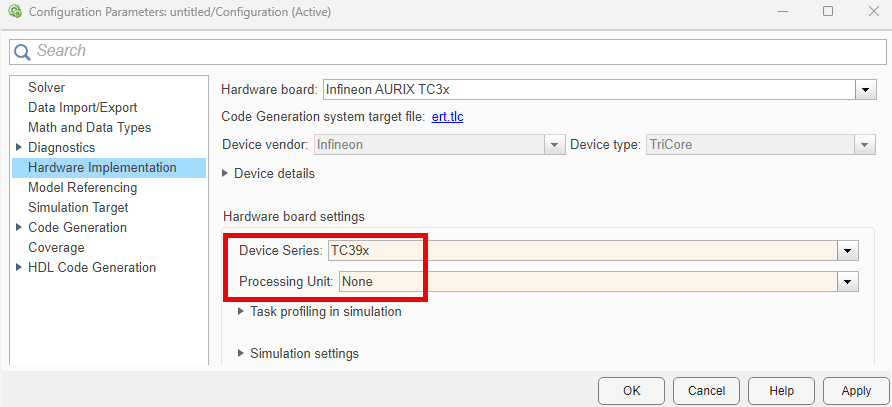

Set the Processing Unit parameter of the top-model to

Nonefor SoC workflow. Ensure the Device Series parameter in Configuration Parameters window of top-level model and referenced models match to avoid conflict.

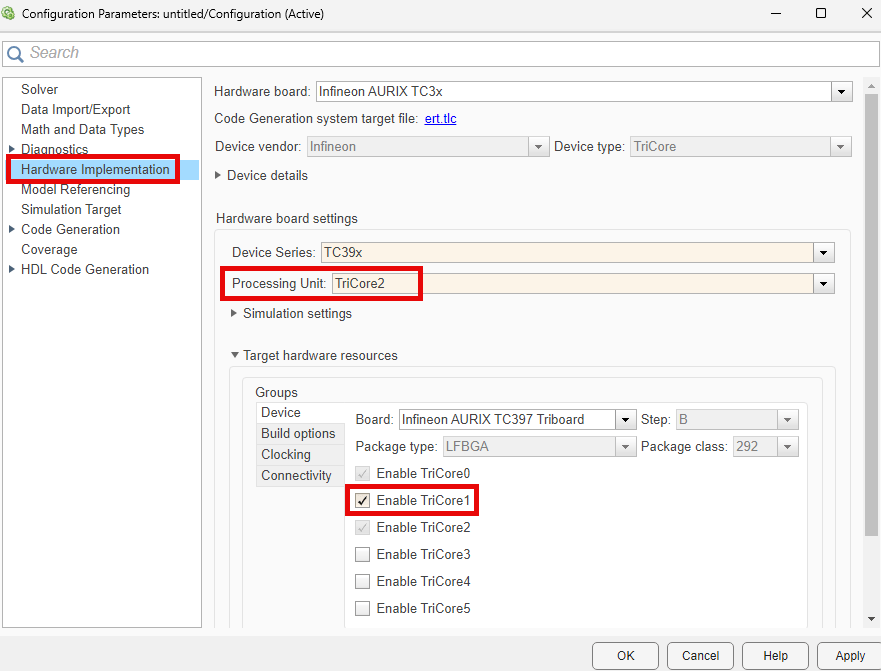

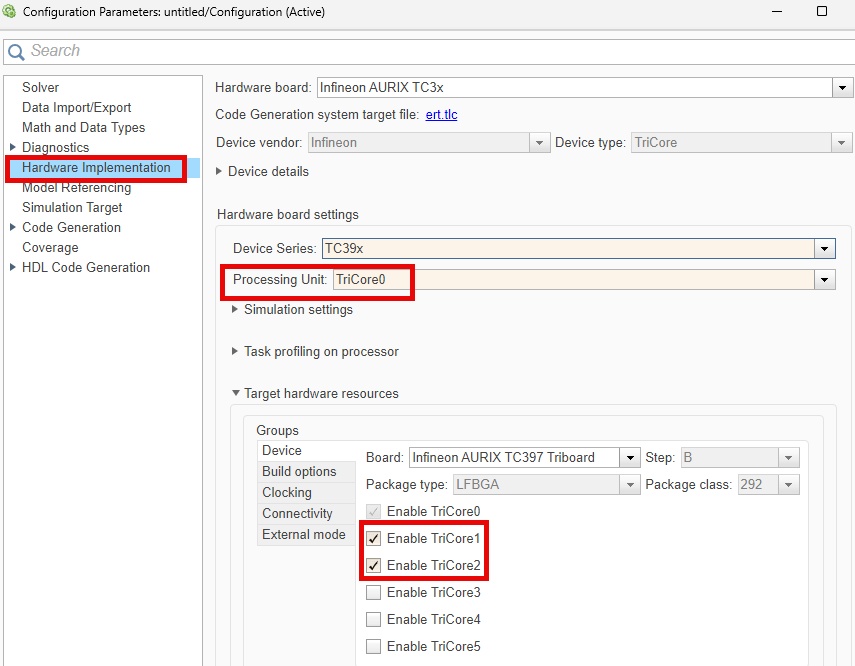

To ensure that the TriCore 0 referenced model has information about other participating cores, select the Enable CPU 1 and Enable CPU 2 parameters in the Configuration Parameters window of the TriCore 0 referenced model.

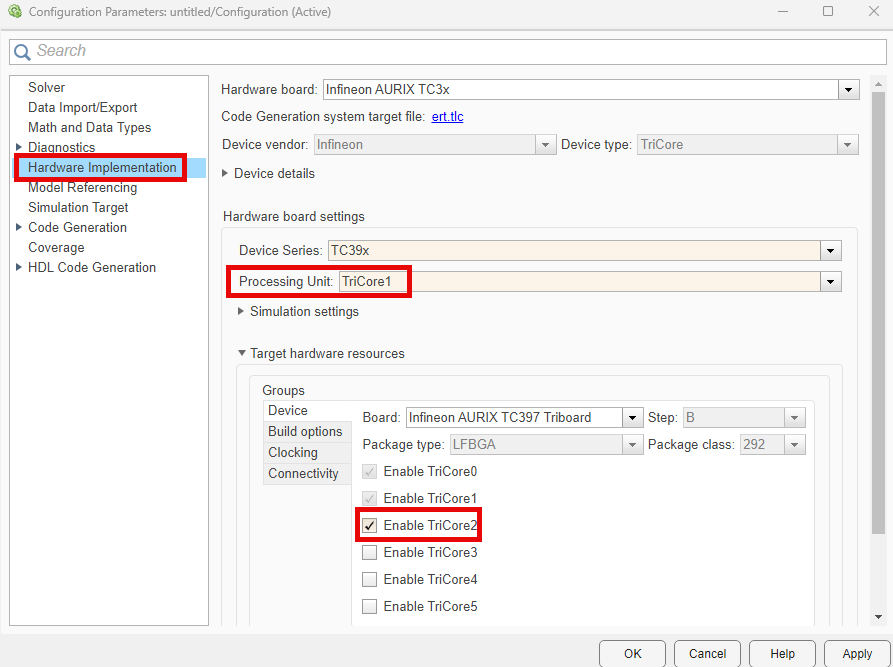

Select the Enable CPU 2 parameter in the referenced model using the

TriCore1processing unit. By default, the Enable CPU 0 parameter is always selected in all the referenced models as the TriCore 0 core is the principal core.

Select the Enable CPU 1 parameter in the referenced model using the

TriCore 2processing unit.