使用 Infineon AURIX 进行多核仿真和代码生成

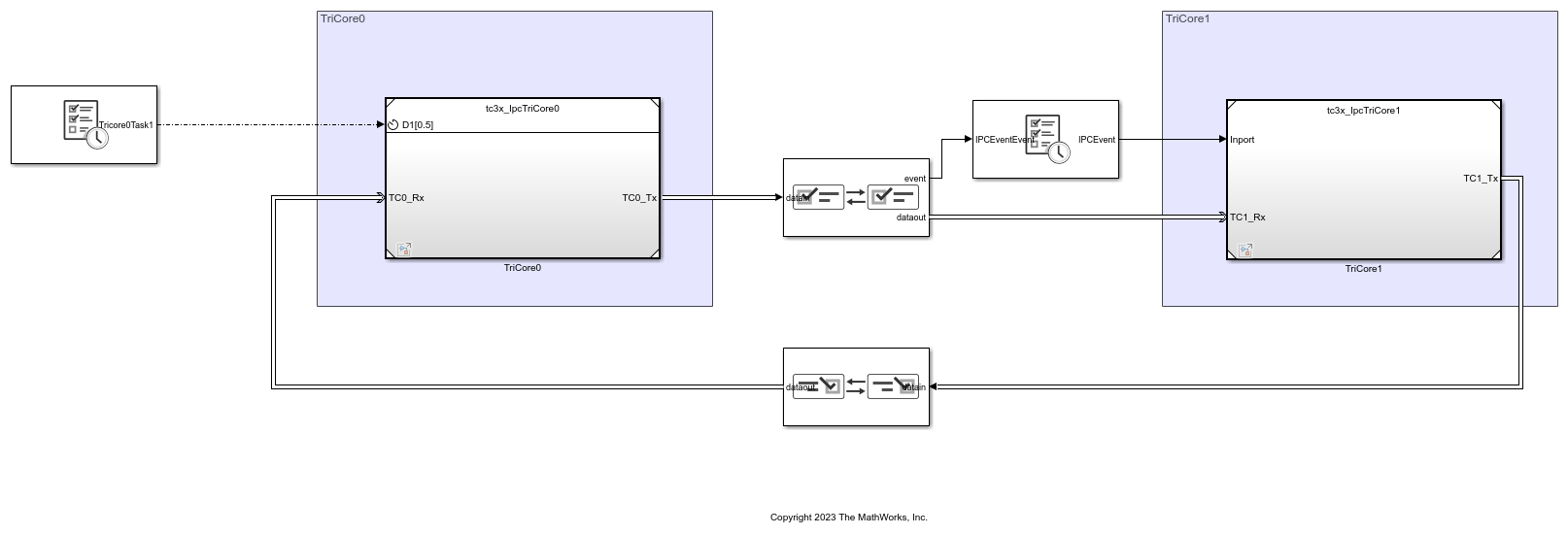

Infineon AURIX TC3x 微控制器具有多个同构 TriCore® 处理单元。TC39x 系列由六个 TriCore(TriCore0 到 TriCore5)组成,TC38x 系列由四个 TriCore(TriCore0 到 TriCore3)组成,TC37x 系列由三个 TriCore(TriCore0 到 TriCore2)组成。TriCore0 是主核,其余核为辅助核。

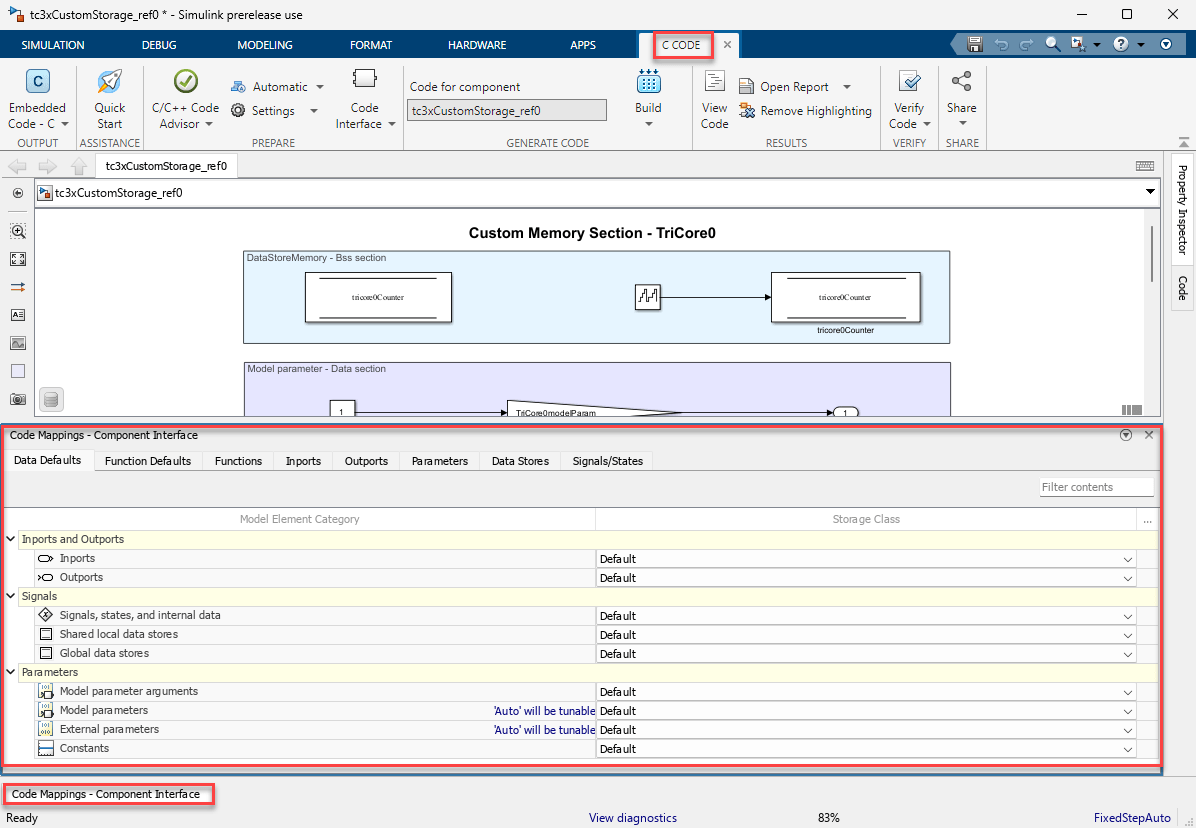

您可以在可用的核上运行不同的模型,也可以对复杂模型进行分区以便在多个核上同时运行,从而实现设计模块化。Interprocess Data Channel 模块处理多个核之间的通信。在对多核模型进行仿真后,您可以使用 SoC 构建器工具在 Infineon AURIX TC3x 硬件板上部署生成的代码,并使用 Infineon 的 One Eye 工具监控来自硬件的信号。

使用 SoC 构建器工具生成可执行文件、代码和对硬件板进行编程。请参阅Getting Started with Multicore Modeling and Targeting for Infineon AURIX TC3x Microcontrollers示例,了解如何验证、编译和运行多核模型,以生成可执行文件、代码和对 Infineon AURIX TC4x 硬件板进行编程。

模块

工具

主题

- Top-Level Models Using TriCores of Infineon AURIX

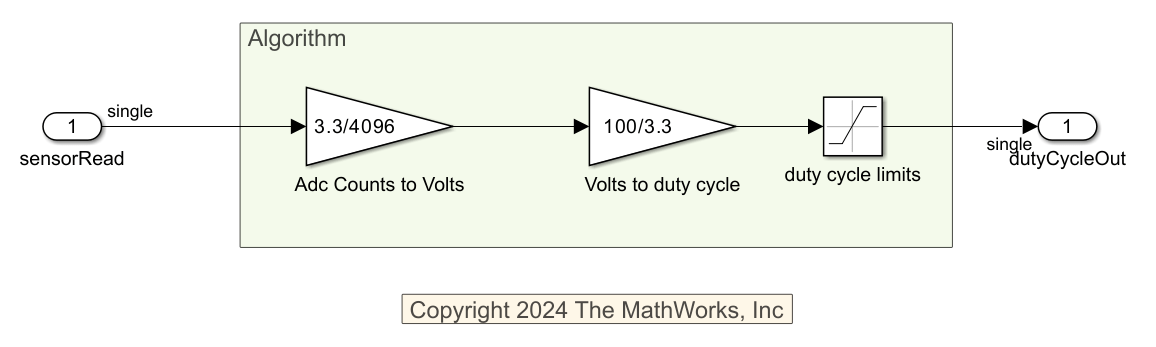

Simulate, and generate code for top-level models with referenced models using TriCores of Infineon AURIX microcontrollers.

- Generate Code and Deploy Using SoC Builder

Generate code and run it on the target hardware board using the SoC Builder tool.

- Generate Software Executables for Multicore Models

Generate ELF file for all participating homogenous cores of Infineon AURIX.

- Task Duration

Set the execution time or duration of a task in Task Manager block.

- What is Task Execution?

Learn the definition of task execution and task life-cycle in a processor.

- Task Execution Playback Using Recorded Data

Replay task execution timing using recorded task timing data from previous simulations or processors.