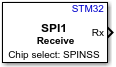

SPI Receive

Libraries:

STM32 Microcontroller Blockset /

STM32F1xx Based Boards

STM32 Microcontroller Blockset /

STM32F2xx Based Boards

STM32 Microcontroller Blockset /

STM32F3xx Based Boards

STM32 Microcontroller Blockset /

STM32F4xx Based Boards

STM32 Microcontroller Blockset /

STM32F7xx Based Boards

STM32 Microcontroller Blockset /

STM32G0xx Based Boards

STM32 Microcontroller Blockset /

STM32G4xx Based Boards

STM32 Microcontroller Blockset /

STM32H5xx Based Boards

STM32 Microcontroller Blockset /

STM32H7xx Based Boards

STM32 Microcontroller Blockset /

STM32L4xx Based Boards

STM32 Microcontroller Blockset /

STM32L5xx Based Boards

STM32 Microcontroller Blockset /

STM32U5xx Based Boards

STM32 Microcontroller Blockset /

STM32WBxx Based Boards

Description

The SPI Receive block outputs the values received as an

[Nx1] array of the uint8,

uint16 or uint32 data types.

The SPI Receive block supports synchronous, serial peripheral input/output port communications between the processor and external peripherals or other controllers. The block can run in either peripheral or controller mode. In controller mode, the SPI_MOSI pin transmits data, and the SPI_MISO pin receives the data. When controller mode is selected, the SPI initiates the data transfer by sending a serial clock signal (SPICLK), which is used for the entire serial communications link. Data transfers are synchronized to this SPICLK, which enables both controller and peripheral to send and receive data simultaneously. The maximum frequency for the clock is one quarter of the processor clock frequency.

The SPI device receives data and places the data in the receive buffer. The SPI Receive block reads the data from the receive buffer. In controller mode, SPI Transmit the block initiates SPI transmission by writing data to the transmit buffer. Then, the data received in the receive buffer is read by the SPI Receive block. In peripheral mode, the SPI Receive block is used to read the data in the receive buffer, which is received from the controller. Then, the data is written into the transmit buffer using the SPI Transmit block. From the transmit buffer, the data is sent to the controller.

The SPI receive interrupt is configured for a specific hardware board by navigating to Configuration Parameters > Hardware Implementation > Target hardware resources.

SPI Module is configured in STM32CubeMX project.

Launch the STM32CubeMX project. For more information, see Configure STM32CubeMX with Simulink.

Navigate to Pinout & Configuration > Connectivity > SPI#

Note

You can run a Simulink® model containing SPI Receive block in Connected IO mode on STM32 Processor based boards. For more information, see Communicate with Hardware Using Connected IO.

Verify that these settings meet the requirements of your application.

Note

The following are the limitations for SPI block:

Number of bytes of data to be sent to the transmit block should be less than the FIFO length.

On running SPI Controller Transfer block in Monitor & Tune, you might observe the junk data. To resolve, reconnect and start Monitor & Tune.

If SPI Controller Transfer block is used in a model don’t use the SPI Transmit and SPI Receive blocks for the same module.

Avoid using same modules of SPI in multiple tasks, which can lead to issues.

SPI blocks do not support Master Receive Only, Slave Receive Only, Master Transmit Only, and Slave Transmit only for SPI mode configuration in STM32CubeMX file.

Examples

Ports

Output

Parameters

Extended Capabilities

Version History

Introduced in R2023a