CORDIC Sigmoid HDL Optimized

库:

Fixed-Point Designer HDL Support /

Math Operations

描述

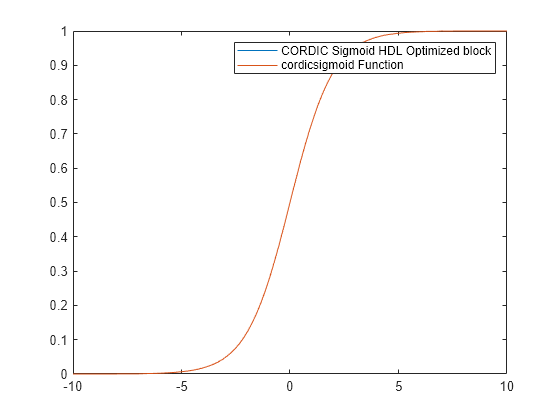

CORDIC Sigmoid HDL Optimized 模块返回 u 的 sigmoid 激活,使用针对 HDL 代码生成进行了优化的 CORDIC 实现进行计算。

示例

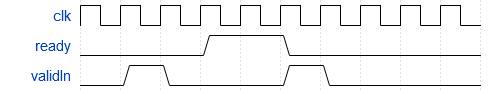

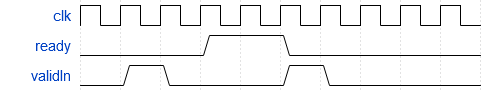

端口

输入

输出

算法

参考

[1] Volder, Jack E. “The CORDIC Trigonometric Computing Technique.” IRE Transactions on Electronic Computers EC-8, no. 3 (Sept. 1959): 330–334.

[2] Andraka, Ray. “A Survey of CORDIC Algorithm for FPGA Based Computers.” In Proceedings of the 1998 ACM/SIGDA Sixth International Symposium on Field Programmable Gate Arrays, 191–200. https://dl.acm.org/doi/10.1145/275107.275139.

[3] Walther, J.S. “A Unified Algorithm for Elementary Functions.” In Proceedings of the May 18-20, 1971 Spring Joint Computer Conference, 379–386. https://dl.acm.org/doi/10.1145/1478786.1478840.

[4] Schelin, Charles W. “Calculator Function Approximation.” The American Mathematical Monthly, no. 5 (May 1983): 317–325. https://doi.org/10.2307/2975781.

扩展功能

版本历史记录

在 R2024a 中推出