HDL Code Generation and FPGA Synthesis from Simulink Model

This example shows how you can generate HDL code for a simple counter model and synthesize the generated code on a Xilinx® FPGA by using the Simulink® HDL Workflow Advisor. To create this model, see Create HDL-Compatible Simulink Model.

HDL Workflow Advisor is not available in Simulink Online™.

Simulink HDL Workflow Advisor

The HDL Workflow Advisor guides you through generating HDL code for a Simulink subsystem and the FPGA design process, such as:

Checking the model for HDL code generation compatibility and automatically fixing incompatible settings.

Generation of HDL code, a test bench, and scripts to build and run the code and test bench.

Generation of cosimulation or SystemVerilog DPI test benches and code coverage (requires HDL Verifier™).

Synthesis and timing analysis through integration with third-party synthesis tools.

Back-annotation of the model with critical path information and other information obtained during synthesis.

Complete automated workflows for selected FPGA development target devices and the Simulink Real-Time™ FPGA I/O workflow, including FPGA-in-the-loop simulation.

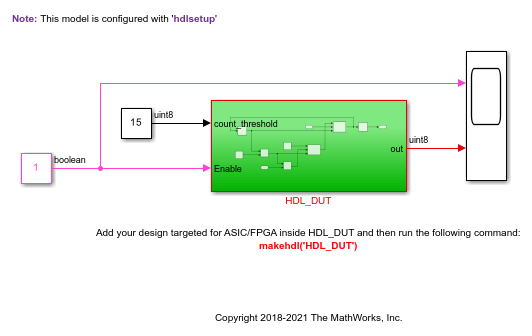

Simple Counter Model

This model counts up from zero to a threshold value of 15, then wraps back to zero. You can change the threshold value by changing the value of the Constant block connected to the count_threshold port. The Enable port specifies whether the counter counts upward or holds the previous value. You can change the counter action by changing the value of the Constant block connected to the Enable port. A value of 1 indicates that the counter counts upward. A value of 0 holds the previous count value.

Set Up Tool Path

To synthesize your design on a target platform, before you open the HDL

Workflow Advisor and run the workflow, set up the path to your synthesis tool.

This example uses Xilinx

Vivado®, so you must have already installed Xilinx

Vivado. To set the tool path, use the hdlsetuptoolpath function.

hdlsetuptoolpath('ToolName','Xilinx Vivado','ToolPath',... 'C:\Xilinx\Vivado\2024.1\bin\vivado.bat');

hdlsetuptoolpath. To learn about

the latest supported tools, see HDL Language Support and Supported Third-Party Tools and Hardware.If you want to generate HDL code but not synthesize your design, you do not have to set the tool path.

Open the HDL Workflow Advisor

To start the HDL Workflow Advisor from a Simulink model,

In the Apps tab, select HDL Coder.

Select the DUT Subsystem in your model,

HDL_DUT, and make sure this name appears in the Code for option on the HDL Code tab. To remember the selection, pin this option. Click Workflow Advisor.

When you open the HDL Workflow Advisor, the code generator might warn that the project folder is incompatible. To open the Advisor, select Remove and continue.

The HDL Workflow Advisor displays a group of tasks in the left pane grouped by folders. Expanding the folders shows available tasks in each folder. Selecting a task or folder displays information about that task or folder in the right pane. The right pane has simple controls for running the task to several parameters and options for code or test bench generation, and contains a display area for status messages and other task results.

To learn more about each individual task, right-click that task, and select What's This?.

Generate HDL Code

In the Set Target > Set Target Device and Synthesis Tool step, for Synthesis tool, select

Xilinx Vivadoand select Run This Task. See also Workflows in HDL Workflow Advisor. To generate HDL code but not synthesize the code, leave the Synthesis tool setting toNo Synthesis Tool Specified.

In Set Target Frequency task, specify a target frequency that you want the design to achieve by using the Target Frequency parameter. For this example, set Target Frequency (MHz) to

200.To check you model for code generation compatibility, run the tasks in the Prepare Model For HDL Code Generation folder. Right-click the Check Sample Times task and select Run to Selected Task. If running a task generates a warning, select Modify All, and rerun the task.

To modify code generation , use the tasks in Set Code Generation Options. For example, to customize the target HDL language and the target code generation folder, use the Set Basic Options task. After you make changes, click Apply.

To generate code, right-click the Generate RTL Code and Testbench task and select Run to Selected Task.

Perform FPGA Synthesis and Analysis

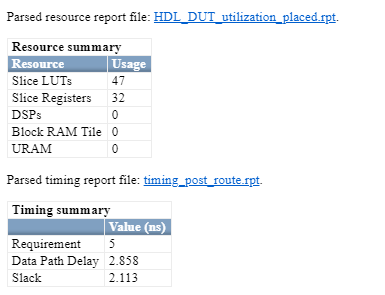

In the FPGA Synthesis and Analysis > Perform Synthesis and P/R > Run Implementation task, clear Skip this task and click Apply. Then, right-click this task and select Run to Selected Task.

The task displays the amount of resources consumed by the design and the data path delay. The slack is the difference between the required time and the arrival time for a combinational path. In this case, the slack is a positive value, which means that data arrived much earlier than the required time.

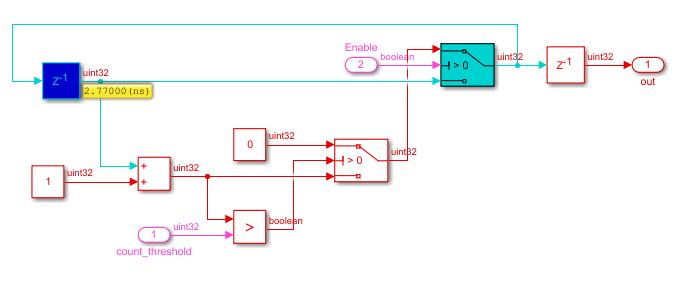

Right-click Annotate Model with Synthesis Result and select Run to Selected Task. If you chose

Microchip Libero SoCas the Synthesis tool, the Annotate Model with Synthesis Result task is not available. To see the critical path, run the workflow to synthesis and then open the timing reports. For more information on analyzing pre- or post-routing timing information and visually highlights critical paths in your model, see Annotate Model with Synthesis Result.

View the annotated critical path in the model.

Critical path is a combinational path between the input and output that has

the maximum delay. The critical path delay for the counter model is

2.77ns. The data path delay reported in Run

Implementation task is more than the critical path because it

accounts for routing delays on the target FPGA. To save resources, optimize the

critical path, and improve timing of your design on the target FPGA, use speed

and area optimizations in HDL Coder™. To learn more, see Introduction to Optimizations in HDL Coder.

Run Workflow at Command Line with a Script

To run the HDL workflow at the MATLAB® command prompt, export the Workflow Advisor settings to a script. To export to script, in the HDL Workflow Advisor window, select File > Export to Script. In the Export Workflow Configuration dialog box, enter a file name and save the script. See Run HDL Workflow with a Script.

See Also

hdladvisor | hdlsetuptoolpath | makehdl