HDL Coder 快速入门

HDL Coder™ 通过从 MATLAB® 函数、Simulink® 模型和 Stateflow® 图生成可移植、可综合的 Verilog®、SystemVerilog 和 VHDL® 代码,支持 FPGA、SoC 和 ASIC 的高层设计。您可以将生成的 HDL 代码用于 FPGA 编程、ASIC 原型构建和生产设计。

HDL Coder 包括工作流顾问,可用于在 Xilinx®、Intel® 和 Microchip 板上通过生成的代码自动进行原型构建,并为 ASIC 和 FPGA 工作流生成 IP 核。您可以针对速度和面积进行优化,突出显示关键路径,并在综合之前生成资源利用率估计值。HDL Coder 提供 Simulink 模型与生成的 Verilog、SystemVerilog 和 VHDL 代码之间的可追溯性,因而支持对遵循 DO-254 及其他标准的高完整性应用进行代码验证。

教程

- 创建 HDL 兼容的 Simulink 模型

创建一个模型并检查 HDL 代码生成的兼容性。

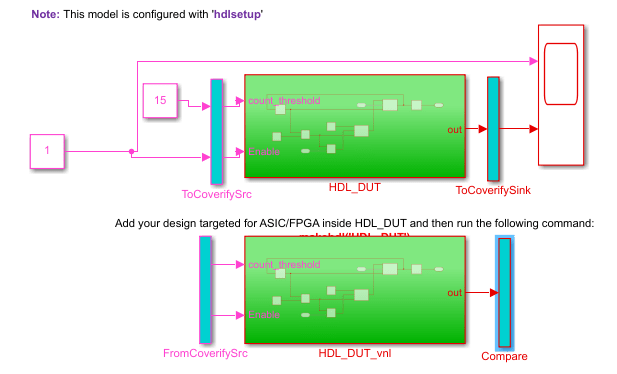

- Verify Generated HDL Code from Simulink Model

Generate an HDL test bench to verify the VHDL or Verilog Code.

- HDL Code Generation and FPGA Synthesis from Simulink Model

Generate code and synthesize your Simulink design on the target FPGA.

关于 HDL 代码生成

- Basic HDL Code Generation Workflow

Follow the workflow for HDL code generation and FPGA synthesis from MATLAB and Simulink algorithms.

精选示例

视频

HDL Coder 概述

使用 HDL Coder 生成用于 FPGA 和 ASIC 设计的 VHDL 和 Verilog 代码

使用 Simulink 在 FPGA 或 ASIC 上部署 MATLAB 算法

了解如何通过 Simulink、Fixed-Point Designer™ 和 HDL Coder 采用 MATLAB DSP 算法并以 FPGA 或 ASIC 为目标