从 MATLAB 进行基本 HDL 代码生成和 FPGA 综合

此示例说明如何创建一个 HDL Coder™ 工程,为您的 MATLAB® 设计生成代码,并综合 HDL 代码。在此示例中,您将:

创建一个 MATLAB HDL Coder 工程。

将设计和测试平台文件添加到工程。

为 MATLAB 设计启动 HDL 工作流顾问。

运行定点转换和 HDL 代码生成。

从 MATLAB 测试平台生成 HDL 测试平台。

使用 HDL 仿真器验证生成的 HDL 代码。您可以使用 ModelSim® 或 Xilinx® Vivado® Simulator 作为仿真工具。

使用综合工具综合生成的 HDL 代码。此示例使用 Xilinx® Vivado® 作为工具。

FIR 滤波器 MATLAB 设计

MATLAB 设计 mlhdlc_sfir 是简单的对称 FIR 滤波器。

design_name = 'mlhdlc_sfir'; testbench_name = 'mlhdlc_sfir_tb';

查看 MATLAB 设计。

open(design_name);

%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%% % MATLAB design: Symmetric FIR Filter % % Introduction: % % We can reduce the complexity of the FIR filter by leveraging its symmetry. % Symmetry for an n-tap filter implies, coefficient h0 = coefficient hn-1, % coefficient, h1 = coefficient hn-2, etc. In this case, the number of % multipliers can be approximately halved. The key is to add the % two data values that need to be multiplied with the same coefficient % prior to performing the multiplication. % % Key Design pattern covered in this example: % (1) Filter states represented using the persistent variables % (2) Filter coefficients passed in as parameters % Copyright 2011-2019 The MathWorks, Inc. %#codegen function [y_out, delayed_xout] = mlhdlc_sfir(x_in,h_in1,h_in2,h_in3,h_in4) % Symmetric FIR Filter % declare and initialize the delay registers persistent ud1 ud2 ud3 ud4 ud5 ud6 ud7 ud8; if isempty(ud1) ud1 = 0; ud2 = 0; ud3 = 0; ud4 = 0; ud5 = 0; ud6 = 0; ud7 = 0; ud8 = 0; end % access the previous value of states/registers a1 = ud1 + ud8; a2 = ud2 + ud7; a3 = ud3 + ud6; a4 = ud4 + ud5; % multiplier chain m1 = h_in1 * a1; m2 = h_in2 * a2; m3 = h_in3 * a3; m4 = h_in4 * a4; % adder chain a5 = m1 + m2; a6 = m3 + m4; % filtered output y_out = a5 + a6; % delayout input signal delayed_xout = ud8; % update the delay line ud8 = ud7; ud7 = ud6; ud6 = ud5; ud5 = ud4; ud4 = ud3; ud3 = ud2; ud2 = ud1; ud1 = x_in; end

FIR 滤波器 MATLAB 测试平台

MATLAB 测试平台 mlhdlc_sfir_tb 通过使用有代表性的输入范围来测试滤波器设计。查看 MATLAB 测试平台 mlhdlc_sfir_tb。

open(testbench_name);

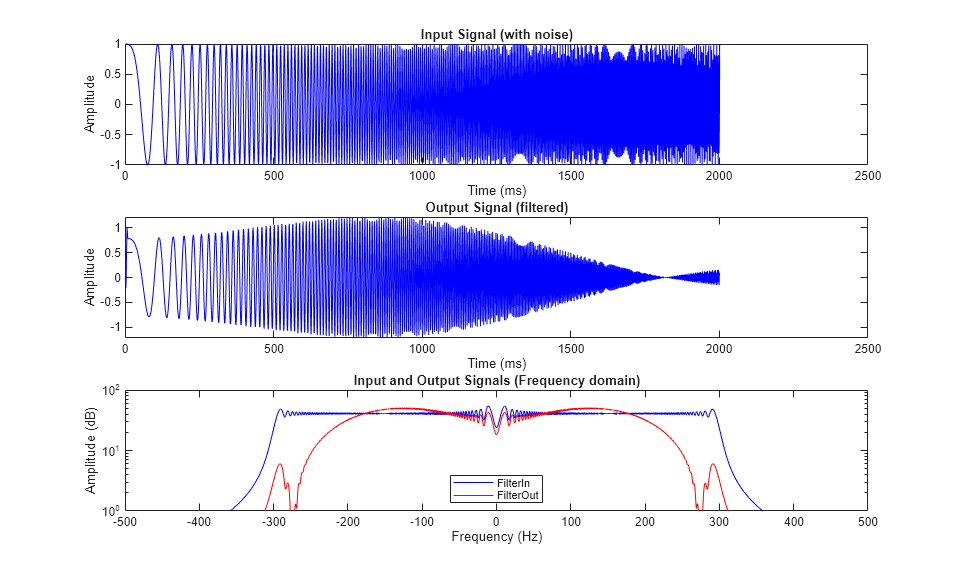

%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%% % MATLAB test bench for the FIR filter %%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%% % Copyright 2011-2019 The MathWorks, Inc. clear mlhdlc_sfir; T = 2; dt = 0.001; N = T/dt+1; sample_time = 0:dt:T; df = 1/dt; sample_freq = linspace(-1/2,1/2,N).*df; % input signal with noise x_in = cos(2.*pi.*(sample_time).*(1+(sample_time).*75)).'; % filter coefficients h1 = -0.1339; h2 = -0.0838; h3 = 0.2026; h4 = 0.4064; len = length(x_in); y_out = zeros(1,len); x_out = zeros(1,len); for ii=1:len data = x_in(ii); % call to the design 'mlhdlc_sfir' that is targeted for hardware [y_out(ii), x_out(ii)] = mlhdlc_sfir(data, h1, h2, h3, h4); end figure('Name', [mfilename, '_plot']); subplot(3,1,1); plot(1:len,x_in,'-b'); xlabel('Time (ms)') ylabel('Amplitude') title('Input Signal (with noise)') subplot(3,1,2); plot(1:len,y_out,'-b'); xlabel('Time (ms)') ylabel('Amplitude') title('Output Signal (filtered)') freq_fft = @(x) abs(fftshift(fft(x))); subplot(3,1,3); semilogy(sample_freq,freq_fft(x_in),'-b'); hold on semilogy(sample_freq,freq_fft(y_out),'-r') hold off xlabel('Frequency (Hz)') ylabel('Amplitude (dB)') title('Input and Output Signals (Frequency domain)') legend({'FilterIn', 'FilterOut'}, 'Location','South') axis([-500 500 1 100])

测试原始 MATLAB 算法

为避免运行时错误,请使用测试平台对设计进行仿真。

mlhdlc_sfir_tb

设置 HDL 仿真器和综合工具路径

如果您要综合生成的 HDL 代码,在使用 HDL Coder 生成代码之前,请设置您的综合工具路径。要设置综合工具的路径,请使用 hdlsetuptoolpath 函数。例如,如果您的综合工具是 Xilinx Vivado:

hdlsetuptoolpath('ToolName','Xilinx Vivado','ToolPath',... vivadopath);

您必须已安装 Xilinx Vivado。要检查您的 Xilinx Vivado 综合工具设置,请通过运行以下命令启动此工具:

!vivado

如果您要使用 HDL 测试平台对生成的 HDL 代码进行仿真,可以使用诸如 ModelSim® 之类的 HDL 仿真器。您必须已安装 HDL 仿真器。

创建 HDL Coder 工程

要创建一个 HDL Coder 工程,请执行以下操作:

1.通过运行以下命令创建一个工程:

coder -hdlcoder -new sfir_project

2.对于 MATLAB Function,添加 MATLAB 设计 mlhdlc_sfir。添加 mlhdlc_sfir_tb.m 作为 MATLAB 测试平台。

3.点击 Autodefine types 并对 MATLAB 设计使用推荐的类型。代码生成器通过运行测试平台来推断数据类型。

创建算法和测试平台的定点版本

点击工作流顾问按钮以打开工作流顾问。您会看到定义输入类型任务已通过。

运行定点转换任务。定点转换工具在右窗格中打开。

当您运行定点转换时,为了建议浮点数据类型的小数长度,HDL Coder 使用默认字长。在本教程中,默认字长是 14。顾问提供的默认仿真最小值/最大值的安全裕度为 0%。顾问通过此安全系数调整数据的范围。例如,值 4 指定您要使范围增大至少 4%。另请参阅Floating-Point to Fixed-Point Conversion。

选择代码生成选项并生成 HDL 代码

在生成 HDL 代码之前,如果您要将代码部署到目标平台上,请指定综合工具。在代码生成目标任务中,将工作流保留为 Generic ASIC/FPGA 并指定 Xilinx Vivado 作为综合工具。如果您没有看到综合工具,请点击刷新列表。运行此任务。

在 HDL 代码生成任务中,通过使用此任务右侧的选项卡,您可以指定其他代码生成选项。

默认情况下,HDL Coder 生成 VHDL® 代码。要生成 Verilog 或 SystemVerilog 代码,请在目标选项卡的语言部分选择

Verilog或SystemVerilog。要生成具有注释和可追溯性链接的代码生成报告,请在编码风格选项卡中,选择包括 MATLAB 源代码作为注释和生成报告。

要优化您的设计,您可以使用分布式流水线优化。在优化选项卡中,为输入流水线和输出流水线指定

1,然后选择分布流水线寄存器。要了解详细信息,请参阅。点击运行以生成 Verilog 或 SystemVerilog 代码。

检查日志窗口并点击链接以浏览生成的代码和报告。

生成 HDL 测试平台并仿真生成的代码

HDL Coder 会生成一个 HDL 测试平台,使用 HDL 仿真器运行该 HDL 测试平台,并验证 HDL 仿真是否与定点 MATLAB 仿真的数值和延迟一致。

要生成 HDL 测试平台并仿真生成的代码,请在 HDL 验证 > HDL 测试平台验证任务中执行以下操作:

在输出设置选项卡中,选择生成 HDL 测试平台。

要仿真生成的测试平台,请将仿真工具设置为

ModelSim或Xilinx Vivado Simulator。您必须已安装所需的仿真工具并在 MATLAB 系统路径中设置该工具。要指定在单独的文件中生成 HDL 测试平台代码和测试平台数据,请在测试平台选项选项卡中,选择多文件测试平台。

点击运行按钮。

该任务生成一个 HDL 测试平台,然后使用选定仿真工具仿真定点设计,并生成编译报告和仿真报告。

综合生成的 HDL 代码

HDL Coder 在目标平台上综合 HDL 代码,并根据您指定的目标器件为您的设计生成面积和时序报告。

要综合生成的 HDL 代码,请执行以下操作:

1.运行创建工程任务。

此任务为 HDL 代码创建一个 Xilinx Vivado 综合工程。HDL Coder 在下一个任务中使用此工程来综合设计。

2.选择并运行运行综合任务。

此任务在后台启动综合工具,打开综合工程,编译 HDL 代码,综合设计,并生成网表以及面积和时序报告。

3.选择并运行运行实现任务。

此任务在后台启动综合工具,对设计运行布局布线,并生成用于关键路径分析和源模型回注的布线前和布线后时序信息。