创建 HDL 兼容的 Simulink 模型

此示例说明如何创建一个适用于 HDL 代码生成的 Simulink® 模型。要创建一个与 HDL 代码生成兼容的 MATLAB® 算法,请参阅编写 MATLAB 代码以生成高效 HDL 和 HLS 代码的规范。

该模型是一个简单的计数器算法,它向上计数,并在达到您指定的上限后绕回到零。要直接打开模型而不执行这些步骤,请参阅简单计数器模型。

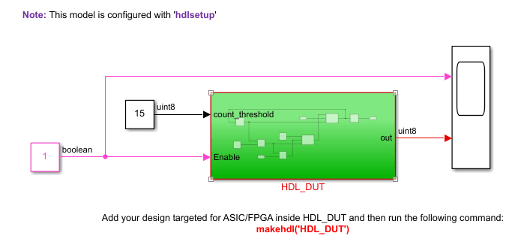

使用空白 DUT 模板

要创建一个 HDL 兼容的 Simulink 模型,请使用空白 DUT 模板。该模板使用 hdlsetup 函数针对 HDL 代码生成进行了预配置。

在 MATLAB 工具条上,点击

按钮。

按钮。在 Simulink 起始页中,导航到 HDL Coder 部分,然后选择空白 DUT 模板。

将模型以文件名

hdlcoder_simple_up_counter.slx保存在可写的工作文件夹中。

空白 DUT 模板有 HDL_DUT 子系统,该子系统对应于您要为其生成 HDL 代码的在测设计 (DUT)。为了验证 DUT 功能,模板包含一个在 HDL_DUT 子系统外部的测试平台,该测试平台向 DUT 提供输入并记录输出值。请参阅Partition Model into DUT and Test Bench。

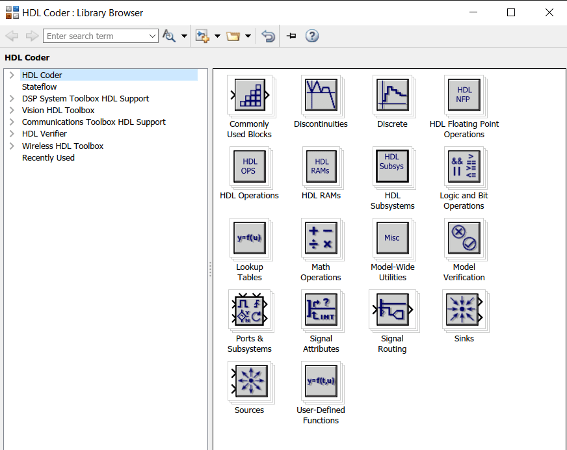

从 HDL Coder 库中选择模块

要设计您的计数器算法,请使用 HDL Coder 模块库中的模块。此库中的模块已针对 HDL 代码生成进行了预配置。要过滤 Simulink 库浏览器以显示支持 HDL 代码生成的模块库,请执行以下操作:

在 App 选项卡上,选择 HDL Coder。

从 HDL Code 选项卡中,选择 HDL 模块属性 > 打开 HDL 模块库。

或者,在命令行中输入 hdllib。

hdllib

您可以通过 Simulink 使用 HDL Coder 库中的模块。如果您没有 HDL Coder™,您可以在模型中对这些模块进行仿真,但无法生成 HDL 代码。

您可以在以下模块库中找到 HDL 支持的其他模块:

DSP System Toolbox HDL Support

Communications Toolbox HDL Support

Vision HDL Toolbox

Wireless HDL Toolbox

要将库浏览器还原到默认视图,请在库浏览器中点击  按钮。或者,在命令行中输入:

按钮。或者,在命令行中输入:

hdllib('off')为 DUT 开发算法

双击

HDL_DUT子系统。将模块从 HDL Coder 库拖到您的模型中。下表列出了要添加到模型以设计计数器的模块。要了解模块的功能并指定其模块参数,请双击该模块。模块 库 模块数量 模块参数 Constant Sources 2常量值:1 和 0

输出数据类型:uint8

Switch Signal Routing 2首个输入传递条件::u2 > 阈值 Delay Discrete 2延迟长度:1 Sum Math Operations 1累加器数据类型:继承:与第一个输入相同 Relational Operator Logic and Bit Operations 1关系运算符:> 将输入端口

In1和In2分别重命名为count_threshold和Enable。将模块放置在您的模型中并连接它们。

Enable 信号指定计数器是否从先前值向上计数。当 Enable 信号为逻辑高电平时,计数器进行从零到 count_threshold 值的向上计数。当 out 的值等于 count_threshold 值时,计数器绕回到零并重新开始计数。当 Enable 信号变为逻辑低电平时,计数器保持先前的值。

为设计创建测试平台

导航到模型的顶层并更改输入设置。

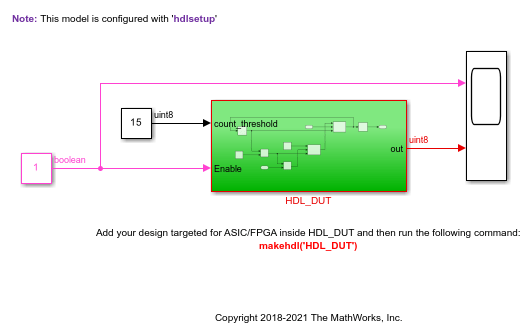

将 Constant 模块输入更改为

count_threshold:此输入指示计数器计数所达到的最大值。此示例说明如何设计一个 4 位向上计数器。将常量值设置为15(2^4 - 1),并将输出数据类型设置为uint8。然后,此 Constant 模块的输出数据类型与

HDL_DUT子系统内部的 Constant 模块的输出数据类型匹配。将 Counter Free-Running 模块输入更改为

Enable:删除 Counter Free-Running 模块。将此模块替换为 Constant 模块,后者的值为1,输出数据类型设置为boolean,并且采样时间为1。

另请参阅创建简单模型。

上一节显示了您按照上述步骤创建的 hdlcoder_simple_up_counter.slx 模型。要在 MATLAB 中打开该模型,请点击打开模型按钮。

简单计数器模型

打开此模型以查看简单的计数器。该模型从零向上计数到阈值,然后绕回到零。阈值设置为 15。要更改阈值,请更改 count_threshold 端口的输入值。Enable 信号指定计数器是向上计数还是保持先前的值。值为 1 表示计数器持续向上计数。

仿真并验证设计功能

将模型的停止时间设置为 50。通过点击  按钮对您的模型进行仿真。要查看仿真结果,请打开模型顶层的 Scope 模块。

按钮对您的模型进行仿真。要查看仿真结果,请打开模型顶层的 Scope 模块。

仿真结果显示 Enable 信号生成常量值 1。out 信号从 0 计数到 15,绕回到零,然后再次向上计数。

从 Simulink 模型生成 HDL 代码

在生成 HDL 代码之前,您可以验证模型设置是否与 HDL 代码生成兼容。此示例中使用的计数器模型与 HDL 代码生成兼容。要验证和更新模型以与 HDL 兼容,请使用 HDL 代码顾问。请参阅Check HDL Compatibility of Simulink Model Using HDL Code Advisor。

另请参阅

hdllib | checkhdl | hdlsetup | hdlcodeadvisor