HDL IP 核生成

在目标硬件平台上部署生成的 IP 核

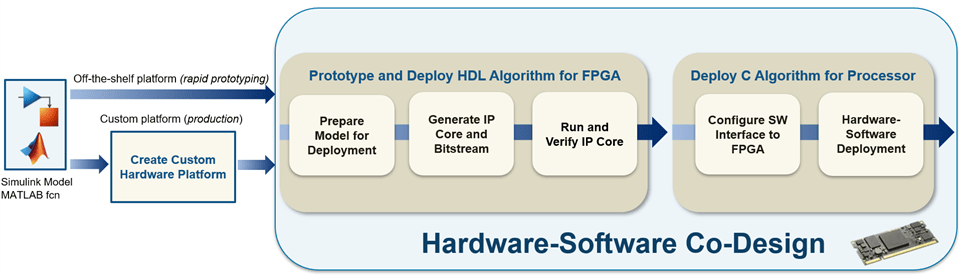

生成可重用的 HDL IP 核以设计可部署在硬件或软硬件组合上的系统。通过以下形式部署您的 MATLAB® 或 Simulink® 设计:

作为片上系统 (SoC) 平台(如 Xilinx® Zynq®、Intel® SoC 或 Microchip SoC)上的硬件和软件。

在独立 FPGA 板(如 Intel FPGA 或 Xilinx FPGA 板)上。

在具有单独 FPGA 和处理器的平台(如 Simulink Real-Time™ 目标机与 FPGA I/O 板)上。

如果使用的是 SoC 平台或具有单独 FPGA 和处理器的平台,您可以对设计进行分区,生成以 FPGA 结构为目标的硬件和在目标平台的嵌入式处理器上运行的软件。

有关工作流的更多详细信息,请参阅Targeting FPGA & SoC Hardware Overview。有关特定硬件平台的更多详细信息,请参阅HDL Coder 支持的硬件。

类别

- IP 核生成基础知识

学习 IP 核生成基础知识

- 为 IP 核生成准备模型

为 IP 核生成准备模型或 MATLAB 函数

- 生成 IP 核和比特流

生成 HDL IP 核和比特流,包含用于部署在独立 FPGA 板、Speedgoat® I/O 模块、Xilinx Zynq-7000 平台、Intel SoC 器件或 Microchip SoC 器件上的 HDL 代码

- 运行和验证生成的 IP 核

在目标 FPGA 器件上原型化、仿真和验证生成的 IP 核

- 为软件接口配置 IP 核

配置软件接口模型以连接设计的 IP 核并部署到目标硬件的嵌入式处理器

- 用于软硬件部署的 IP 核生成

在目标硬件上部署和运行软硬件模型

- 在自定义硬件上部署 IP 核

通过定义自定义板和参考设计将生成的 IP 核集成到目标 SoC 器件、Speedgoat I/O 模块或独立的 FPGA 板中