IP 核生成基础知识

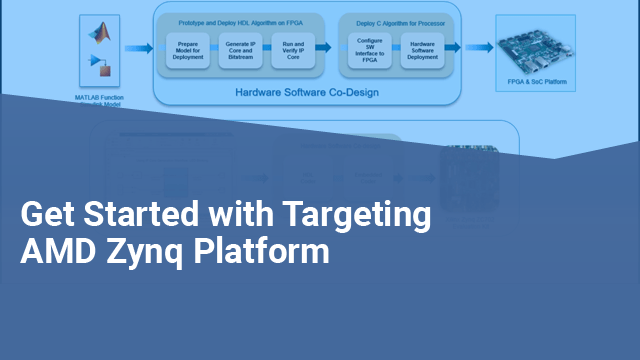

使用 HDL Coder™ 以硬件为目标时,您可以根据目标按照一个具有两个不同起点的工作流进行操作:

要对现成的、预先存在的硬件平台进行快速原型构建,请使用预先存在的板和参考设计为 FPGA 原型化和部署 HDL 算法,并启动软硬件协同设计工作流。

对于以自定义设备为目标的生产工作流,创建一个自定义硬件平台。然后按照软硬件协同设计工作流进行操作。

有关更多详细信息,请参阅Targeting FPGA & SoC Hardware Overview和Hardware-Software Co-Design Workflow for SoC Platforms。

工具

| IP 核编辑器 | Configure IP core for target hardware (自 R2023b 起) |

类

hdlcoder.WorkflowConfig | Configure HDL code generation and deployment workflows |

主题

- Targeting FPGA & SoC Hardware Overview

High-level steps for targeting an FPGA or SoC platform.

- Hardware-Software Co-Design Workflow for SoC Platforms

High-level workflow steps for targeting an SoC platform.

- Comparison of IP Core Generation Techniques

Decide how to best generate an IP core for your Simulink design and migrate from the HDL Workflow Advisor to the Simulink toolstrip to generate an IP core. (自 R2023b 起)

- Comparison of IP Core Deployment and Verification Techniques

Decide how to best verify and deploy your IP core and migrate from the HDL Workflow Advisor to the Simulink toolstrip to generate a reference design. (自 R2023b 起)

- Getting Started with the HDL Workflow Advisor

Learn the basics of the HDL Workflow Advisor and how to run various tasks.

- Run HDL Workflow with a Script

Export, import, or configure an HDL Workflow CLI command script.

- Workflows in HDL Workflow Advisor

Learn about the HDL Workflow Advisor and various workflows you can choose and platforms you can target.