Comparison of IP Core Generation Techniques

To generate an IP core interactively from a Simulink® design, you can use:

The HDL Workflow Advisor. In releases prior to R2023b, this is the only method to generate an IP core interactively from a Simulink model. See Using the HDL Workflow Advisor.

The Simulink Toolstrip. You can use the HDL Code tab to generate an IP core and use the IP Core editor and the Configuration Parameters dialog box to configure the HDL and IP core settings. To open the HDL Coder app, see HDL Coder.

While both the HDL Workflow Advisor and the Simulink Toolstrip can generate an IP core, each IP core generation method offers different advantages. The HDL Workflow Advisor provides step-by-step instructions that you can apply to new models that are not yet configured for IP core generation. You can also use the HDL Workflow Advisor as a guided workflow if you are new to the IP core generation process. After you generate an IP core and you want to iterate on your design, you can use the Simulink Toolstrip to rapidly prototype and generate an updated IP core with more flexibility, efficiency, and scalability.

IP Core Process Comparison

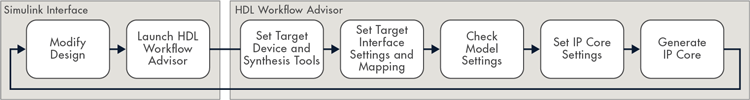

This diagram shows the sequential steps when using the HDL Workflow Advisor to generate an IP core:

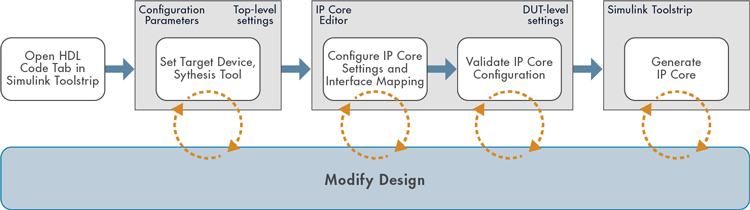

This diagram shows how to rapidly prototype, generate an IP core, and iterate on your design using the Simulink Toolstrip. The general order of steps follows the left-to-right order of the HDL Code tab in the Simulink Toolstrip, but with flexibility to modify your design at any point in the process.

When rapidly prototyping a design, you need to generate an IP core quickly with multiple design iterations. Using the Simulink Toolstrip allows you to quickly to generate an IP core. You can stay inside the Simulink environment, make changes to your design, and update your IP core without needing to re-run any previous options and tasks that you already completed. Using the Simulink Toolstrip gives you greater flexibility to design, configure, and generate an IP core in the order and iteration that best suits your workflow and design process.

This table compares the two processes:

| Workflow Advisor Task | Simulink Toolstrip Step |

|---|---|

Open the HDL Workflow Advisor | Open the HDL Coder app from the Apps tab on the Simulink Toolstrip. In the HDL Code tab, select IP Core from the drop-down button in the Output section. |

1.1 Set Target Device and Synthesis Tools | In the Configuration Parameters dialog box, use the HDL Code Generation > Target pane to set the top-level model settings, such as the target device and synthesis tool settings. |

1.2 Set Target Reference Design | In the Configuration Parameters dialog box, use the HDL Code Generation > Target pane to set the reference design parameters. Note that the Reference design parameters table requires a string input typed directly into the Value box. |

1.3 Set Target Interface | Use the IP Core editor to set DUT-level settings. In the IP Core editor, use the Interface Mapping tab to set the values in the target platform interface table. Use the Interface Settings tab to configure interface-related settings for the IP core, such as the register interface and FPGA data capture properties. Use the Reload IP

core settings Use the

Validate IP core settings |

1.4 Set Target Frequency | In the Configuration Parameter dialog box, use the HDL Code Generation > Target pane to set the Target Frequency parameter. |

2.1 Check Model Settings | On the HDL Code tab of the Simulink Toolstrip, use the HDL Code Advisor button to check your model settings. For more information, see HDL Coder Checks. |

3.1 Set HDL Options | Use the Configuration Parameters dialog box to set HDL code and testbench generation options. |

3.2 Generate RTL Code and IP Core | In the IP Core editor, use the General and Clock Settings tabs to configure general IP core and clock-related settings, respectively. On the HDL Code tab of the Simulink Toolstrip, use the Generate IP Core button to generate an IP core. |

For an example on IP core generation using the Simulink Toolstrip, see Get Started with IP Core Generation from Simulink Model. For an example on IP core generation using the HDL Workflow Advisor, see Generate IP Core with AXI4-Lite Interface.

Limitations

When generating an IP core with either the HDL Workflow Advisor or the Simulink Toolstrip:

You can specify the parameters and settings for an IP core by using the HDL Workflow Advisor, IP Core editor, or Configuration Parameters dialog box. Updating a parameter using one of these options also updates the parameter in the other locations.

When the HDL Workflow Advisor is open, you cannot configure IP core generation settings and options using the Configuration Parameter dialog box or the IP Core editor. To use the Simulink Toolstrip to update an IP core and its settings, first close the HDL Workflow Advisor.