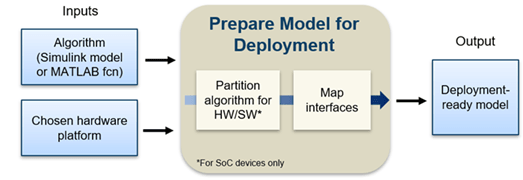

为 IP 核生成准备模型

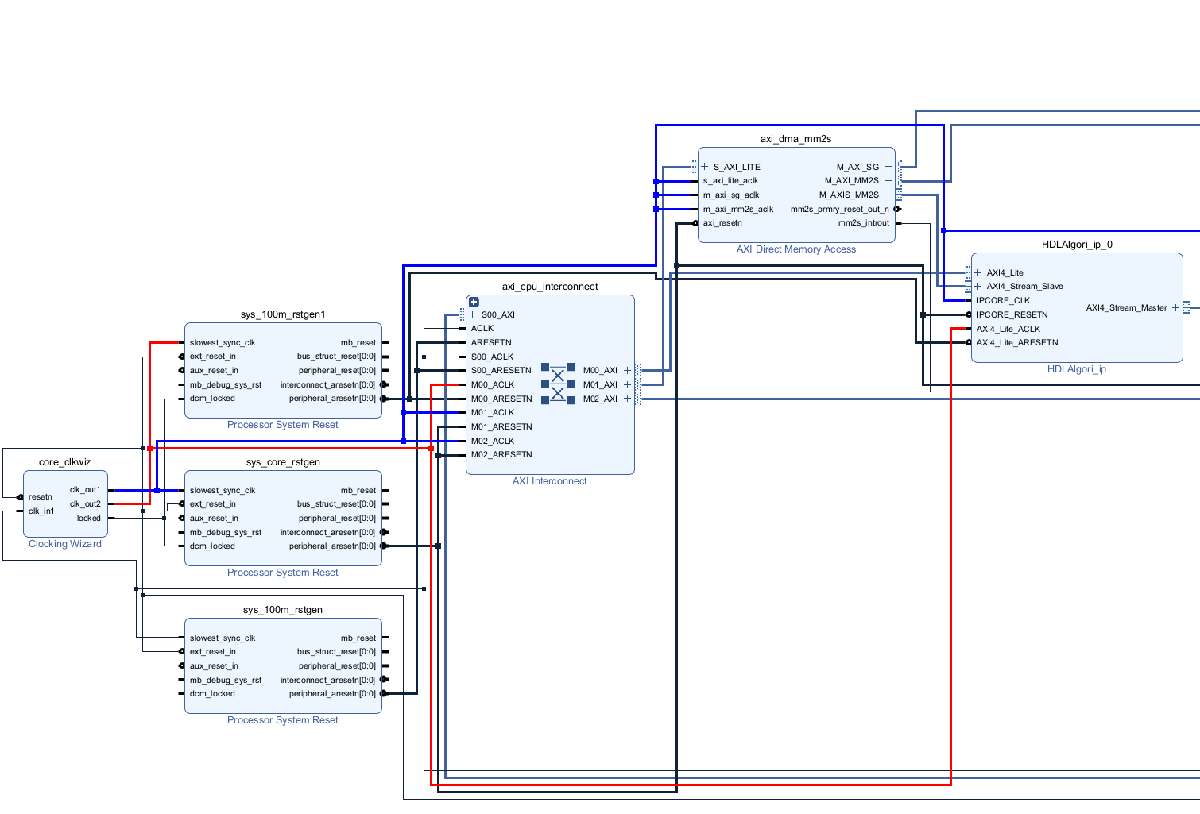

为 IP 核生成准备模型或 MATLAB 函数。输入是 Simulink® 模型或 MATLAB 函数以及选择的硬件平台。输出是一个分区模型,专门为独立 FPGA、SoC 器件板载 FPGA 或 Simulink Real-Time™ 目标机上的 FPGA I/O 板的部署而设计。

有关工作流的更多详细信息,请参阅Targeting FPGA & SoC Hardware Overview。

主题

- Choose an Interface for an IP Core

Choose an interface to connect your IP core to the rest of your design.

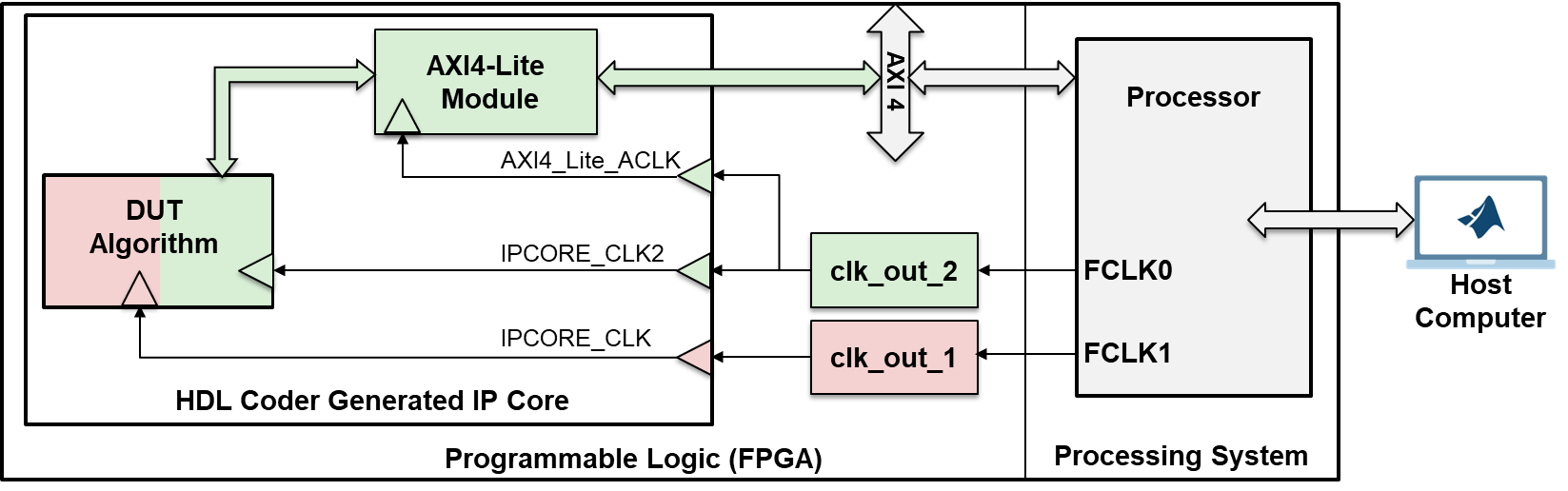

- IP Core Clock Interface

Configure clock inputs for generated IP cores.

- Model Design for AXI4 Register Interface Generation

How to design your model for AXI4 or AXI4-Lite interfaces for scalar, vector ports, bus data types, and read back values.

- IP Core Reset Interface

Learn how HDL Coder™ automatically inserts logic to synchronize global reset signal to IP core clock domain.

- Enable Clock Domain Crossing on AXI4-Lite Interfaces

Connect different clock signals to IP core DUT and AXI4-Lite interfaces. (自 R2024a 起)

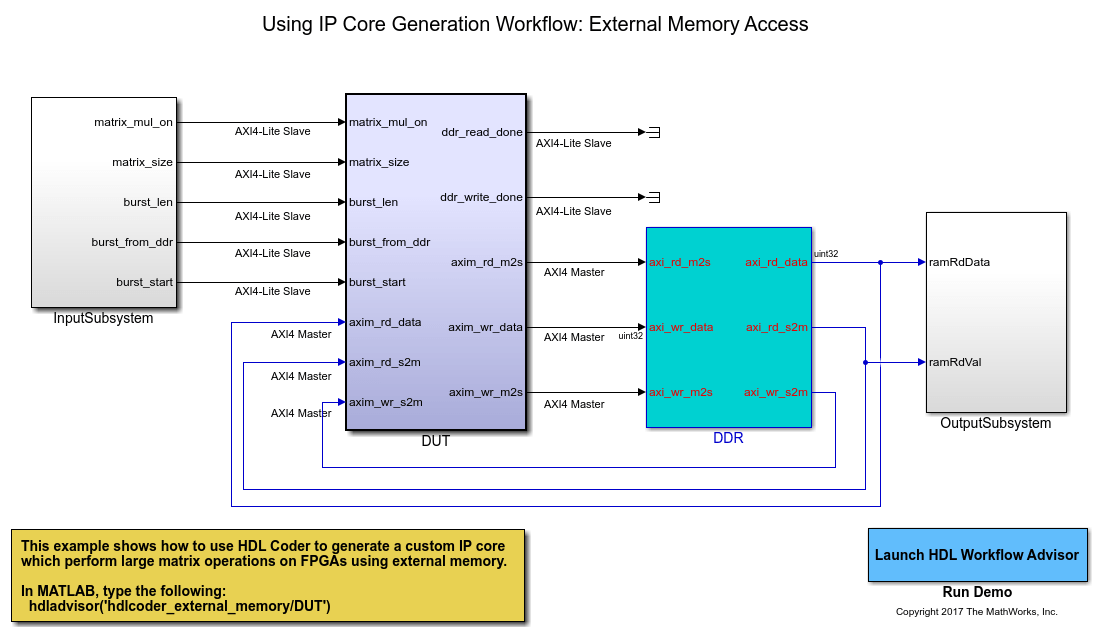

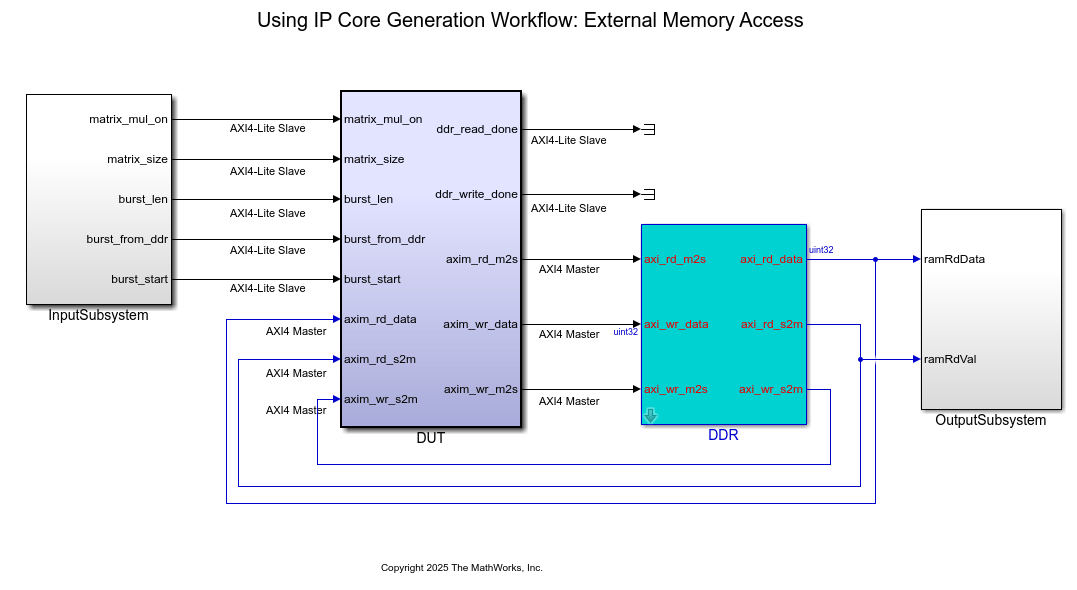

- Map Bus Data Types to a Register Interface

This example shows how to map bus data types to a register interface, generate an HDL IP core with a AXI4 Master interface, perform matrix multiplication in an HDL IP core, and write the output result to DDR memory.

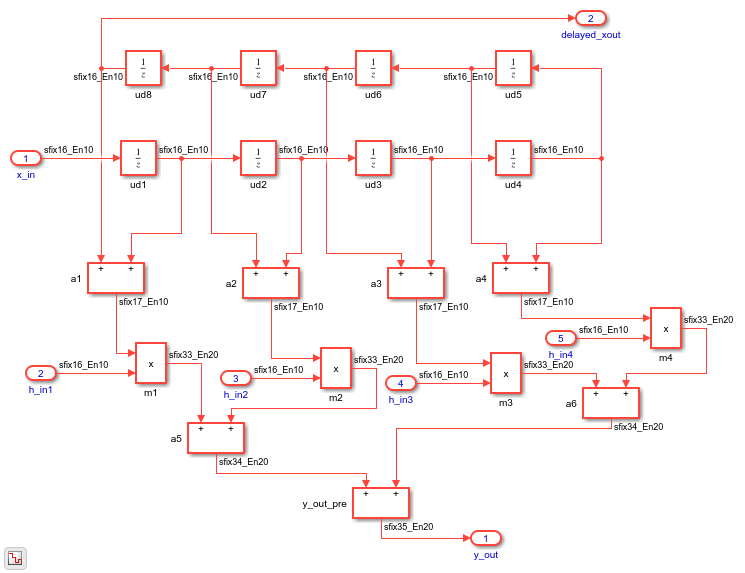

- Model Design for AXI4-Stream Interface Generation

How to design your model for AXI4-Stream vector or scalar interface generation.

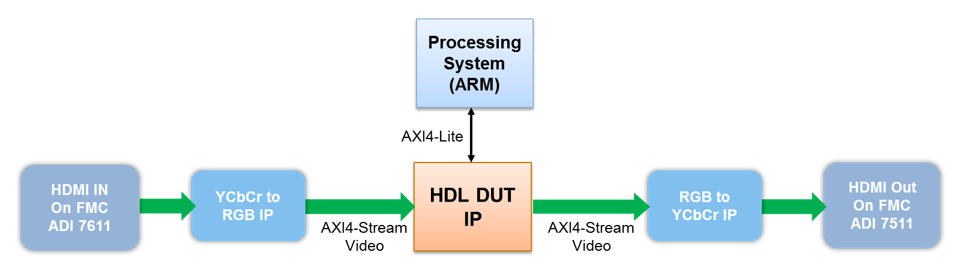

- Model Design for AXI4-Stream Video Interface Generation

How to design your model for IP core generation with AXI4-stream video interfaces.

- Model Design for AXI4 Master Interface Generation

Description of AXI4 Master protocol, and how you can design your model for IP core generation with AXI4-Master interfaces.

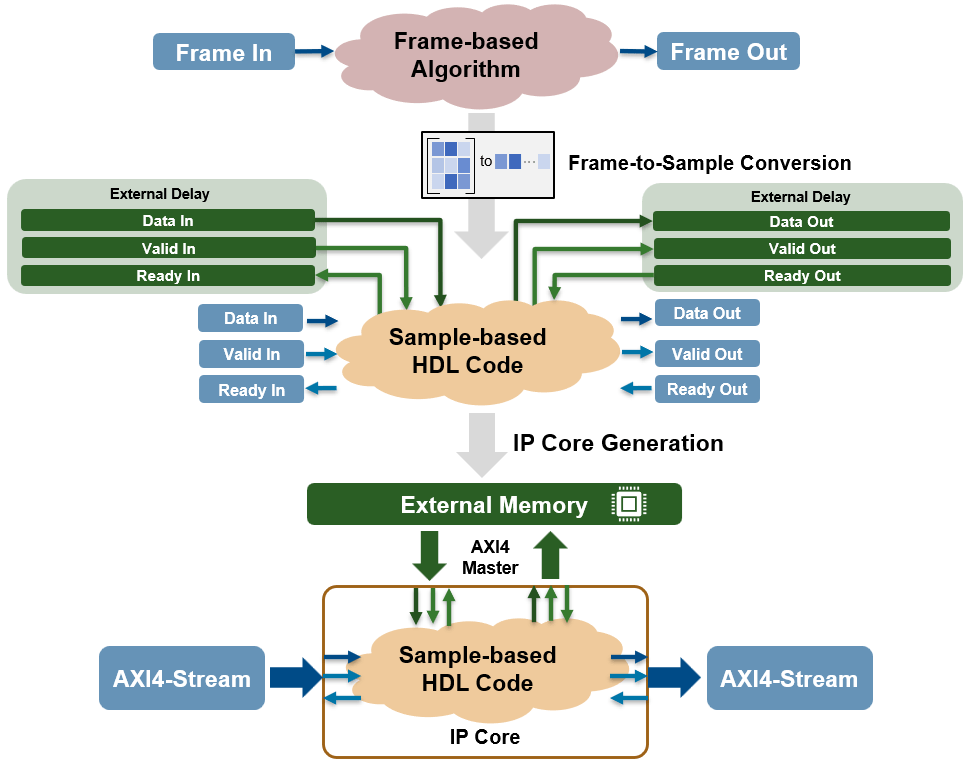

- Model Design for Frame-Based IP Core Generation

How to design your model to use the frame-to-sample optimization for IP core generation.

- Save IP Core Generation and Target Hardware Settings in Model

This example shows how to save your IP core generation and target hardware settings in a Simulink model.