Generate an IP Core for Microchip SoC Platform from MATLAB

Generate an IP Core

To generate a custom IP core to target the Microchip Polarfire® SoC Icicle kit:

Create an HDL Coder™ project containing your MATLAB® design and test bench, or open an existing project.

In the HDL Workflow Advisor, define input type and perform fixed-point conversion.

To learn how to convert your design to fixed-point, see Generate and Synthesize HDL Code for Symmetric FIR Filter Using the HDL Workflow Advisor.

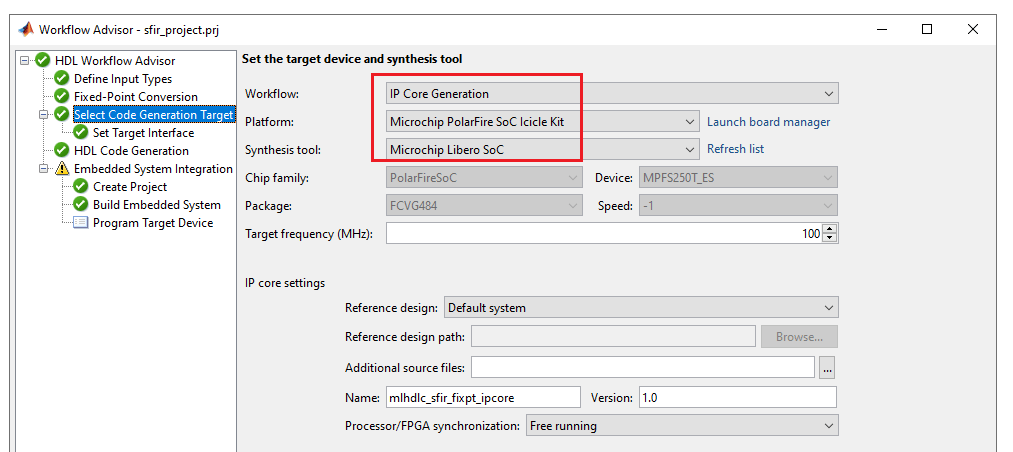

In the HDL Workflow Advisor, in the Select Code Generation Target task:

Workflow: Select

IP Core Generation.Platform: Select your target hardware from the drop-down list.

If you do not see your target hardware in the list, select

Get moreto download the target support package.Additional source files: If you are using an

hdl.BlackBoxSystem object™ to include existing Verilog® or VHDL® code, enter the file names. Enter each file name manually, separated with a semicolon (;), or by using the ... button.

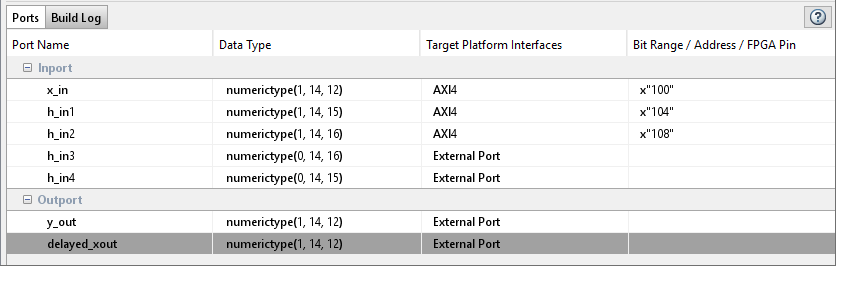

In the Set Target Interface step, for each port, select an option from the Target Platform Interfaces drop-down list.

In the HDL Code Generation step, optionally specify code generation options, then click Run.

In the HDL Workflow Advisor message pane, click the IP core report link to view detailed documentation for your generated IP core.

To learn more about custom IP core generation, see Custom IP Core Generation.

Requirements and Limitations

To map your DUT ports to an AXI4 interface, the input and output ports must:

Have a bit width less than or equal to 32 bits.