Get Started with HDL Workflow Command-Line Interface

This example shows how to use the HDL Workflow Advisor to run HDL workflows from the command line and the Export to script option.

Introduction

This example is a step-by-step guide that helps introduce you to the HDL Workflow Command Line Interface.

Using the HDL Workflow Command Line Interface, you can run the same sequence of steps and control the same configuration settings that are available in the HDL Workflow Advisor for the following workflows:

Generic ASIC/FPGA

IP Core Generation

Simulink® Real-Time™ FPGA I/O

Open the Model

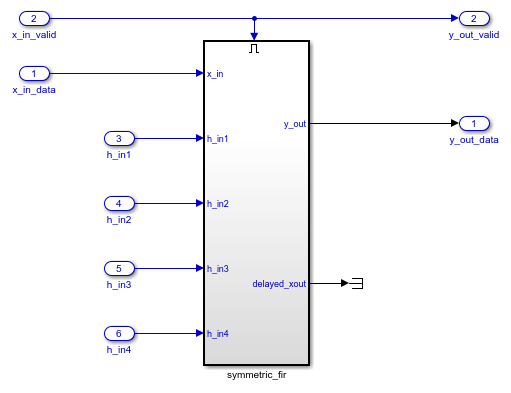

In this example we will use the hdlcoder_sfir_fixed_stream model, but the HDL Workflow Command Line Interface can be used with any model that works with the workflows listed above.

open_system('hdlcoder_sfir_fixed_stream')

Make sure that the desired third party tools are included on the path. For example, to include Vivado installed locally in its default windows location, use the hdlsetuptoolpath command:

>> hdlsetuptoolpath('ToolName', 'Xilinx Vivado', 'ToolPath',vivadopath);Use your own Vivado installation path when you run the command. Next, launch the workflow advisor and select the appropriate subsystem as the DUT.

Setup the Workflow

Use the HDL Workflow Advisor to setup your project with your desired settings, such as a Synthesis Tool and Device. Start by changing the workflow to "Generic ASIC/FPGA" so that we can Annotate the model with synthesis results.

You can also specify high level objectives for the synthesis tool. For example, try setting the tool to "Speed Optimized".

Also, change the "Skip this task" checkbox for Run Implementation so that the exported script runs this step as well.

Export to Script

After all the initial settings have been entered, export your workflow to a script which can be run directly from the command-line for faster design iterations.

Save the file as any name you like. The default will be "hdlworkflow.m". The exported script is shown below:

%-------------------------------------------------------------------------- % HDL Workflow Script % Generated with MATLAB 9.0 (R2016b Prerelease) at 10:40:45 on 31/12/2015 % This script was generated using the following parameter values: % Filename : '/mathworks/devel/sandbox/cberry/work/demo/hdlworkflow.m' % Overwrite : true % Comments : true % Headers : true % DUT : 'hdlcoder_sfir_fixed_stream/DUT' % To view changes after modifying the workflow, run the following command: % >> hWC.export('DUT','hdlcoder_sfir_fixed_stream/DUT'); %-------------------------------------------------------------------------- % Copyright 2018 The MathWorks, Inc. %% Load the Model load_system('hdlcoder_sfir_fixed_stream'); %% Restore the Model to default HDL parameters %hdlrestoreparams('hdlcoder_sfir_fixed_stream/DUT'); %% Model HDL Parameters %% Set Model 'hdlcoder_sfir_fixed_stream' HDL parameters hdlset_param('hdlcoder_sfir_fixed_stream', 'HDLSubsystem', 'hdlcoder_sfir_fixed_stream/DUT'); hdlset_param('hdlcoder_sfir_fixed_stream', 'ReferenceDesign', 'Default system with AXI4-Stream interface'); hdlset_param('hdlcoder_sfir_fixed_stream', 'ResetType', 'Synchronous'); hdlset_param('hdlcoder_sfir_fixed_stream', 'SynthesisTool', 'Xilinx Vivado'); hdlset_param('hdlcoder_sfir_fixed_stream', 'SynthesisToolChipFamily', 'Zynq'); hdlset_param('hdlcoder_sfir_fixed_stream', 'SynthesisToolDeviceName', 'xc7z020'); hdlset_param('hdlcoder_sfir_fixed_stream', 'SynthesisToolPackageName', 'clg484'); hdlset_param('hdlcoder_sfir_fixed_stream', 'SynthesisToolSpeedValue', '-1'); hdlset_param('hdlcoder_sfir_fixed_stream', 'TargetDirectory', 'hdl_prj/hdlsrc'); %% Workflow Configuration Settings % Construct the Workflow Configuration Object with default settings hWC = hdlcoder.WorkflowConfig('SynthesisTool','Xilinx Vivado','TargetWorkflow','Generic ASIC/FPGA'); % Specify the top level project directory hWC.ProjectFolder = 'hdl_prj'; % Set Workflow tasks to run hWC.RunTaskGenerateRTLCodeAndTestbench = true; hWC.RunTaskCreateProject = true; hWC.RunTaskRunSynthesis = true; hWC.RunTaskRunImplementation = false; hWC.RunTaskAnnotateModelWithSynthesisResult = true; % Set properties related to 'RunTaskGenerateRTLCodeAndTestbench' Task hWC.GenerateRTLCode = true; hWC.GenerateRTLTestbench = false; hWC.GenerateCosimulationModel = false; hWC.CosimulationModelForUseWith ='Mentor Graphics ModelSim'; hWC.GenerateValidationModel = false; % Set properties related to 'RunTaskCreateProject' Task hWC.Objective = hdlcoder.Objective.None; hWC.AdditionalProjectCreationTclFiles =''; % Set properties related to 'RunTaskRunSynthesis' Task hWC.SkipPreRouteTimingAnalysis = false; % Set properties related to 'RunTaskRunImplementation' Task hWC.IgnorePlaceAndRouteErrors = false; % Set properties related to 'RunTaskAnnotateModelWithSynthesisResult' Task hWC.CriticalPathSource ='pre-route'; hWC.CriticalPathNumber = 1; hWC.AnnotateModel ='original'; hWC.ShowAllPaths = false; hWC.ShowDelayData = true; hWC.ShowUniquePaths = false; hWC.ShowEndsOnly = false; % Validate the Workflow Configuration Object hWC.validate; %% Run the workflow hdlcoder.runWorkflow('hdlcoder_sfir_fixed_stream/DUT', hWC);

Run workflow from Script

Running the script directly will execute your workflow and output a compact set of runtime messages to the cmd window. If you would like to see detailed synthesis tool output information, click on the relevant "Synthesis tool log: " hyperlink under the desired task header to open this file in the MATLAB® editor.

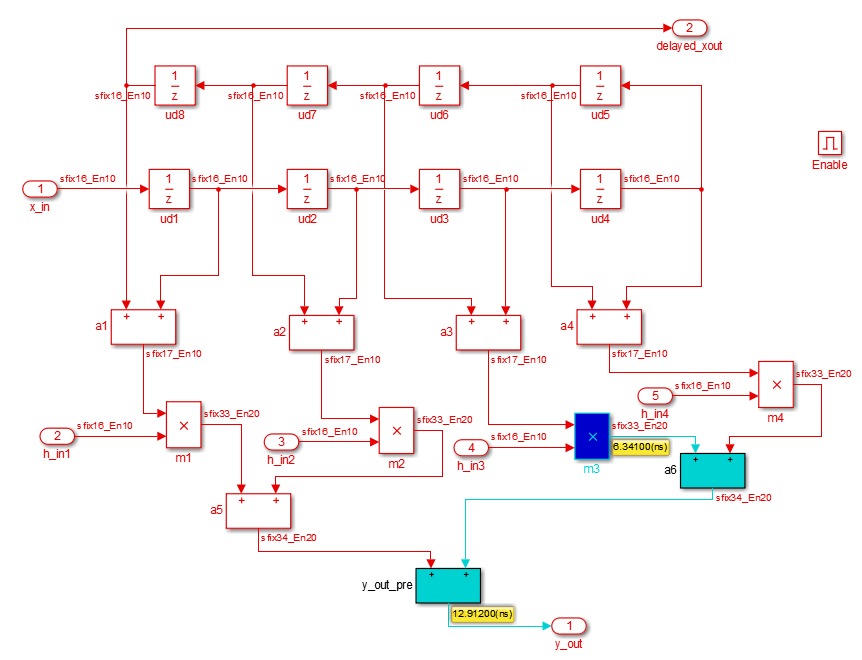

>> hdlworkflow ### Workflow begin. ### ++++++++++++++ Task Generate RTL Code and Testbench ++++++++++++++ ### Generating HDL for 'hdlcoder_sfir_fixed_stream/DUT'. ### Starting HDL check. ### Begin VHDL Code Generation for 'hdlcoder_sfir_fixed_stream'. ### Working on hdlcoder_sfir_fixed_stream/DUT/symmetric_fir as hdl_prj\hdlsrc\hdlcoder_sfir_fixed_stream\symmetric_fir.vhd. ### Working on hdlcoder_sfir_fixed_stream/DUT as hdl_prj\hdlsrc\hdlcoder_sfir_fixed_stream\DUT.vhd. ### Creating HDL Code Generation Check Report DUT_report.html ### HDL check for 'hdlcoder_sfir_fixed_stream' complete with 0 errors, 0 warnings, and 0 messages. ### HDL code generation complete. ### ++++++++++++++ Task Create Project ++++++++++++++ ### Generating Xilinx Vivado 2014.4 project: hdl_prj\vivado_prj\DUT_vivado.xpr ### Synthesis tool log: hdl_prj\hdlsrc\hdlcoder_sfir_fixed_stream\workflow_task_CreateProject.log ### Task "Create Project" successful. ### ++++++++++++++ Task Run Synthesis ++++++++++++++ ### Synthesis tool log: hdl_prj\hdlsrc\hdlcoder_sfir_fixed_stream\workflow_task_RunSynthesis.log ### Task "Run Synthesis" successful. ### ++++++++++++++ Task Run Implementation ++++++++++++++ ### Synthesis tool log: hdl_prj\hdlsrc\hdlcoder_sfir_fixed_stream\workflow_task_RunImplementation.log ### Task "Run Implementation" successful. ### ++++++++++++++ Task Annotate Model with Synthesis Result ++++++++++++++ ### Parsing the timing file... ### Matched Source = 'hdlcoder_sfir_fixed_stream/DUT/symmetric_fir/m3_out1' ### Matched Destination = 'hdlcoder_sfir_fixed_stream/DUT/y_out_data' ### Highlighting CP 1 from 'hdlcoder_sfir_fixed_stream/DUT/symmetric_fir/m3_out1' to 'hdlcoder_sfir_fixed_stream/DUT/y_out_data' ... ### Click here to reset highlighting. ### Workflow complete.

Run workflow interactively

The HDL Workflow Command-Line interface can also be used interactively. For example, after either running the entire script or just the section "Workflow Configuration Settings", the WorkflowConfig object, hWC, will be populated in the workspace:

>> hWC =

GenericTurnkeyConfig with properties:

SynthesisTool: 'Xilinx Vivado'

TargetWorkflow: 'Generic ASIC/FPGA'

ProjectFolder: 'hdl_prj' RunTaskGenerateRTLCodeAndTestbench: true

RunTaskCreateProject: true

RunTaskRunSynthesis: true

RunTaskRunImplementation: true

RunTaskAnnotateModelWithSynthesisResult: true TaskGenerateRTLCodeAndTestbench

GenerateRTLCode: true

GenerateRTLTestbench: false

GenerateCosimulationModel: false

CosimulationModelForUseWith: 'Mentor Graphics ModelSim'

GenerateValidationModel: false TaskCreateProject

Objective: hdlcoder.Objective.SpeedOptimized

AdditionalProjectCreationTclFiles: '' TaskRunSynthesis

SkipPreRouteTimingAnalysis: false TaskRunImplementation

IgnorePlaceAndRouteErrors: false TaskAnnotateModelWithSynthesisResult

CriticalPathSource: 'pre-route'

CriticalPathNumber: 1

AnnotateModel: 'original'

ShowAllPaths: false

ShowDelayData: true

ShowUniquePaths: false

ShowEndsOnly: falseYou can edit this configuration object and then run the workflow with the modified settings. For example, since the task "Run Implementation" was enabled in the previous run, we can change the critical path source to "post-route" with and rerun just the Annotate model task:

>> hWC.clearAllTasks;

>> hWC.RunTaskAnnotateModelWithSynthesisResult = true;

>> hWC.CriticalPathSource = 'post-route';

Then run the modified workflow configurations directly using the hdlcoder.runWorkflow command:

>> hdlcoder.runWorkflow('hdlcoder_led_blinking/led_counter', hWC)

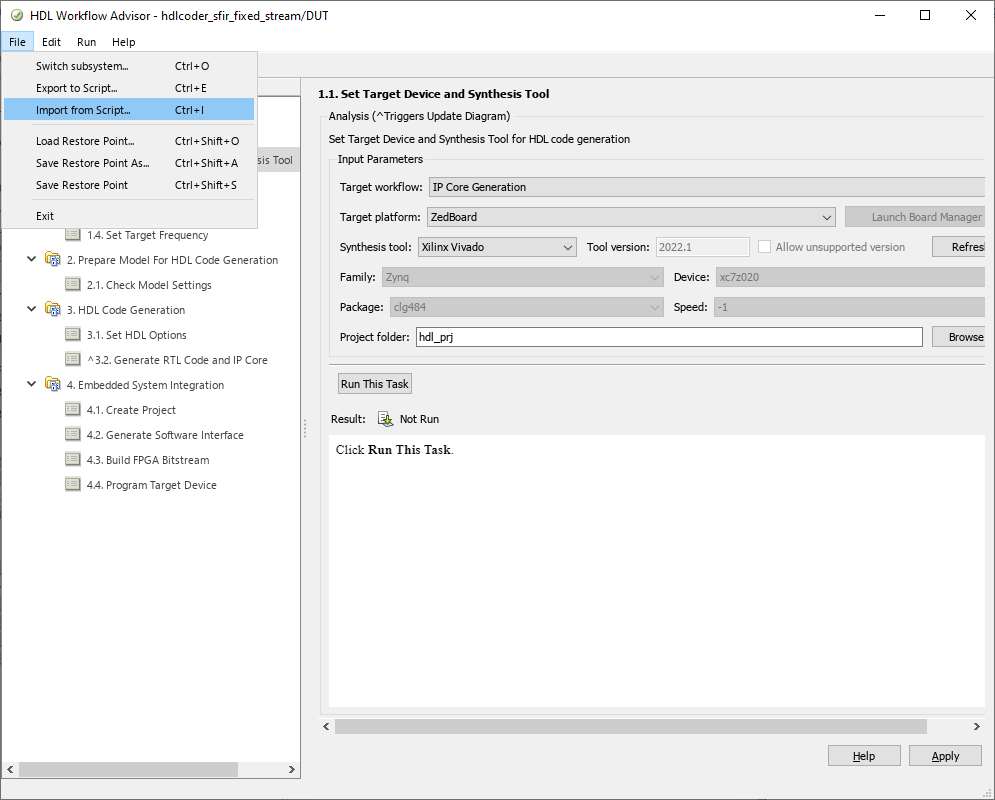

Import script into HDL Workflow Advisor

Any changes you make to the exported script can also be imported back into the HDL Workflow Advisor at any time. To do this, make sure the model loaded is the same as the model used in the script, and select "Import from script" from the File menu.

After importing, all of the script settings will be populated in the HDL Workflow Advisor.

Save the HDL Workflow Command-Line Interface programing script for later use

In certain cases, you can avoid re-running all the steps in the HDL Workflow Advisor just to perform specific tasks in the Advisor. For example, when running the IP Core Generation Workflow, after you generate the FPGA bitstream in the Build FPGA Bitstream Task, the Advisor provides a link that generates a script to run the Program Target Device Task.

Click on the link for hdlworkflow_ProgramTargetDevice.m in Build FPGA Bitstream Task to generate an HDL Workflow Command-Line Interface script which will execute only the Program Target Device Task from an existing hdl_prj directory. Therefore, you can avoid running all the steps in the workflow just to re-program the target device.

The generated script is a standard HDL Workflow CLI script. When running HDL Workflow in command-line interface, the Program Target Device Task can be run independent of previous tasks, as long as the FPGA bitstream is already generated.

As a related note, if you are using the Download programming method in the Program Target Device Task, the HDL Workflow Advisor copies the generated bitstream file onto the SD card on the Zynq or Intel SoC board, so you do not need to re-run the Program Target Device Task to download the bitstream. The FPGA bitstream will be reloaded from the SD card automatically during the Linux boot up process.

Summary

The HDL Workflow Command-Line Interface provides an easily scripted alternative to the graphical HDL Workflow Advisor. Workflows can be setup initially using the HDL Workflow Advisor and then exported to script for iterative or automated use.