Supported Verilog Constructs for HDL Import

Use importhdl

function to import synthesizable Verilog® code into the Simulink® modeling environment. Make sure that the constructs used in the HDL code are

supported by HDL import.

These tables list the supported Verilog constructs that you can use when you import your HDL code. If you use an unsupported construct, HDL import generates an error when parsing the input HDL file. Verilog HDL import can sometimes ignore the presence of certain constructs in the HDL code. To learn more, see the Comments section of the table.

Module Definition and Instantiations

| Verilog Constructs | Supported? | Comments |

|---|---|---|

| Library declaration | No | – |

| Configuration declaration | No | – |

| Module declaration | Yes | Multiple sample rates and multiple clock inputs are not supported. |

| Module parameter port list | Yes | – |

| Port declarations | Yes | INOUT ports are not supported. |

| Module without ports | No | – |

| Local parameter declaration | Yes | – |

| Parameter declaration | Yes | You can use parameters and constants that have a maximum size of

64 bits. By default, the parameter size is

32 bits. |

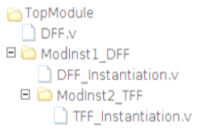

| Module instantiation | Yes |

|

Data Types and Vectors

| Verilog Constructs | Supported? | Comments |

|---|---|---|

| Net declaration (Wire, Supply0, Supply1) | Yes | – |

| Real declaration | No | – |

| String declaration | No | – |

| Vector declaration | Yes | – |

| Array support and array indexing | Yes | – |

| Reg declaration | Yes | – |

| Integer declaration | Yes | – |

Identifiers and Comments

| Verilog Constructs | Supported? | Comments |

|---|---|---|

| Lexical tokens (Whitespace, operator, comment) | Yes | – |

| Identifiers (Simple, Escaped) | Yes | – |

| System Functions ($signed, $unsigned) | Yes | – |

| Attribute instances | No | HDL import ignores these constructs. |

| Comments | No | HDL import ignores these constructs. |

| Numbers (Decimal, Binary, Hexadecimal, and Octal) | Yes | – |

| Compiler directives (`define,`undef, `ifndef, `else if) | Yes | – |

Assignments

| Verilog Constructs | Supported? | Comments |

|---|---|---|

| Continuous assignment | Yes | – |

| Blocking assignment | Yes | -- |

| Nonblocking assignment | Yes | – |

Procedural assignment (Always block) | Yes | – |

Operators

| Verilog Constructs | Supported? | Comments |

|---|---|---|

| Arithmetic operators (+, -, *, **, /, <<<, >>>) | Yes | – |

| Logical operators (<<, >>, !, &&, | |, ==, !=) | Yes | – |

| Relational operators (>, <, >=, <=, ==, !=) | Yes | – |

| Bitwise operators (~, &, |, ^, ~^, ^~) | Yes | – |

| Unary operators (+, -) | Yes | Supported for restricted data types |

| Power operators | Yes | Supported for restricted data types |

| Conditional operators (?:) | Yes | – |

| Concatenation | Yes | – |

| Bit Select | Yes | – |

| Reduction operators (&, ~&, |, ~|, ^, ~^, or ^~) | Yes | – |

For an example that illustrates how to use different operators, see Generate Simulink Model from Verilog Code for Various Operators.

Conditional and Looping Statements

| Verilog Constructs | Supported? | Comments |

|---|---|---|

| If-else statement | Yes | – |

| Conditional operators (?:) | Yes | – |

| For loop | Yes | – |

| Loop Generate construct | Yes | Supports loop generate constructs such as for-generate, case-generate, and if-generate constructs. |

| Conditional Generate construct | No | – |

| Generate region | No | – |

| Genvar declaration | No | – |

| Case statement | Yes | casex and casez statements are also supported. |

Procedural Blocks and Events

| Verilog Constructs | Supported? | Comments |

|---|---|---|

| Task declaration | No | – |

| Initial construct (ROM modeling) | No | – |

| Sequential blocks | Yes | – |

| Block declarations | Yes | – |

| Event control statements | Yes | – |

| Function calls | Yes | HDL import does not support recursive function calls. |

| Task enable | No | – |

Always construct | Yes | – |

| Function declaration | Yes | – |

Other Constructs

| Verilog Constructs | Supported? | Comments |

|---|---|---|

| Gate instantiation | No | – |

| Specparams | No | – |

| Specify block | No | – |

| Semantic verification (unused ports, correct module instantiation) | Yes | – |

| Clock bundle identification | Yes | Multiple sample rates and multiple clock signals are not supported. |

| Register inference | Yes | – |

| Compare to Constant block inference | Yes | – |

| Gain block inference | Yes | – |

| RAM inference | Yes | – |

| ROM inference | No | – |

| Counter inference | No | – |

| Drive strength | No | – |

Limitations and Considerations

Verilog import does not support:

Importing of Verilog files from a read-only folder.

Generation of the preprocessing files in a read-only file system that parses the HDL code you input to the

importhdlfunction.Attribute instances and comments, which are ignored.

(#)delay values, such as

#25, which are ignored.Enumeration data types.

More than one clock signal.

Modules that are multirate.

Recursive module instantiation.

Multiport Switch inference with more than

1024inputs. If you specify more than1024inputs to a Multiport Switch block that gets inferred from the Verilog code, Verilog import generates an error. The error is generated because the Simulink modeling environment does not support more than1024inputs for the block.ROM detection from the Verilog code.

Importing of HDL files that use unsupported dataflow modeling patterns. See Unsupported Verilog Dataflow Patterns.