本页面提供的是上一版软件的文档。当前版本中已删除对应的英文页面。

将 Xilinx System Generator for DSP 与 HDL Coder 结合使用

此示例说明如何将 Xilinx® System Generator for DSP 与 HDL Coder™ 结合使用。

简介

借助 Xilinx System Generator Subsystem 模块,您可以使用 Simulink® 和 Xilinx 提供的模块对设计进行建模,并自动生成集成的 HDL 代码。HDL Coder™ 从 Simulink 模块生成 HDL 代码,并使用 Xilinx System Generator 从 Xilinx System Generator Subsystem 模块生成 HDL 代码。

在此示例中,设计或代码生成子系统包含两部分:一部分是 Simulink 原生模块,另一部分是 Xilinx 模块。Xilinx 模块被分组到 Xilinx System Generator Subsystem sysgendut 中,该子系统位于模型 hdlcoder_slsysgen 顶层的 SLandSysGen 子系统内部。System Generator 针对 Xilinx FPGA 对这些模块进行优化。在设计的其余部分,Simulink 模块和 HDL Coder 提供基于模型的设计功能和 HDL 优化,例如分布式流水线和延迟平衡。

open_system('hdlcoder_slsysgen'); open_system('hdlcoder_slsysgen/SLandSysGen');

对 Simulink® 组件执行模型级优化

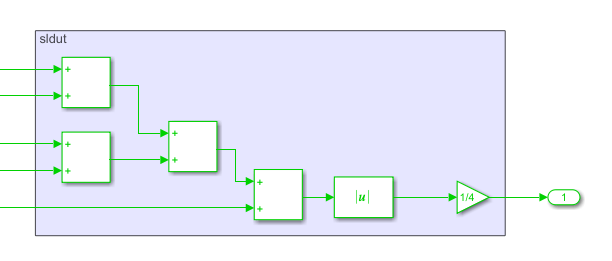

在此示例中,由 SLandSysGen 子系统内部的 sldut 部分指示的求和树是使用 Simulink 模块进行建模的。您可以使用分布式流水线功能来处理速度优化。

分布式流水线可以将流水线寄存器移至求和树中,以减少关键路径而不更改模型函数。其他优化(例如资源复用)也可用,但在此示例中未使用。

open_system('hdlcoder_slsysgen/SLandSysGen');

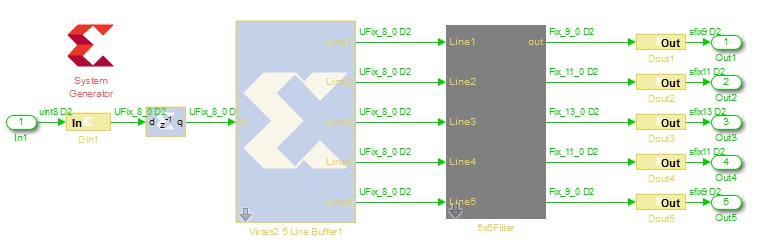

创建 Xilinx System Generator 子系统

要创建 Xilinx System Generator 子系统,请执行以下操作:

将 Xilinx 模块放在一个子系统中,并将 HDL 架构的设置保留为默认值

Module。在子系统的顶层放置一个 System Generator 标记。您可以在 Xilinx System Generator 子系统中包含子系统层次结构,但在层次结构的顶层必须有 System Generator 标记。

open_system('hdlcoder_slsysgen/SLandSysGen/sysgendut');

配置 Gateway In 和 Gateway Out 模块

在每个 Xilinx System Generator 子系统中,您必须将输入和输出端口直接连接到 Gateway In 和 Gateway Out 模块。

Gateway In 模块不能执行非平凡数据类型转换。例如,Gateway In 模块可以在 uint8 和 UFix_8_0 之间进行转换,但不允许更改数据符号、字长或小数长度。

生成 HDL 代码

您可以使用命令行中的 makehdl 或 HDL 工作流顾问来生成 HDL 代码。要使用 makehdl,请执行以下命令:

makehdl('hdlcoder_slsysgen/SLandSysGen');

您也可以像对任何其他模型一样生成测试平台、进行仿真和综合设计。