HDL Test Bench Properties

Generate and customize HDL test bench

With the HDL test bench properties, you can enable and customize test bench generation.

Specify these properties as

name-value arguments to the generatehdl function.

Name is the property name and Value is the

corresponding value. You can specify several name-value arguments in any order as

'Name1',Value1,...,'NameN',ValueN.

For example:

fir = dsp.FIRFilter('Structure','Direct form antisymmetric'); generatehdl(fir,'InputDataType',numerictype(1,16,15), ... 'GenerateHDLTestBench','on','MultifileTestBench','on');

General

GenerateHDLTestBench — Generate HDL test bench

'off' (default) | 'on'

Generate HDL test bench for your HDL filter code, specified as

'off' or 'on'. The test bench

applies generated input stimuli to the generated filter code and compares

the output with stored MATLAB® simulation results.

TestBenchName — File name of generated test bench

filtername_tb

filtername_tbFile name of generated test bench, specified as

filtername_tbfiltername

is the name of the generated VHDL entity or Verilog module. You can

customize this name by setting the Name property. The

coder adds a file type extension to the test bench name, as specified by the

VerilogFileExtension or VHDLFileExtension properties. The test bench file is located

in the folder specified by the TargetDirectory property.

If you specify a value that is a reserved word in the target language, the coder adds the

postfix _rsvd to this value. You can update the postfix value by using

the ReservedWordPostfix

property. For more details, see Resolving HDL Reserved Word Conflicts.

Dependencies

This property applies only when the GenerateHDLTestBench property is set to

'on'.

ErrorMargin — Error margin for test bench comparison in bits

4 (default) | positive integer

Error margin for test bench comparison in bits, specified as

4 or a positive integer. The test bench compares

results with reference signals. These HDL optimizations can generate test

bench code that produces numeric results that differ from the results

produced by the original filter function:

FIRAdderStyleset to'tree'or'pipelined'AddPipelineRegisterswith FIR, asymmetric FIR, and symmetric FIR filters

The error margin specifies an acceptable minimum number of bits by which the numeric results can differ before the test bench issues a warning.

Dependencies

This property applies only when the GenerateHDLTestBench property is set to

'on'.

MultifileTestBench — Generate multifile test bench

'off' (default) | 'on'

Generate multifile test bench, specified as 'off' or

'on'. When this property is set to

'on', the coder generates separate files for test

bench code, helper functions, and test bench data instead of a single file.

The file names are derived from the TestBenchName and TestBenchDataPostfix properties. For example, if the name of

the generated VHDL entity or Verilog module is

my_fir_filt, the default test bench file names are:

my_fir_filt_tb— Test bench codemy_fir_filt_tb_pkg— Helper functions packagemy_fir_filt_tb_data— Test vector data package

The coder appends to these file names the file type extension

defined by the VerilogFileExtension or VHDLFileExtension properties.

Dependencies

This property applies only when the GenerateHDLTestBench property is set to

'on'.

TestBenchDataPostfix — Postfix to file name of test bench data

'_data' (default) | character vector | string scalar

Postfix to file name of test bench data, specified as

'_data', a character vector, or a string scalar. The

coder generates a test bench data file with a file name obtained by

appending this postfix to the TestBenchName property value.

Dependencies

This property applies only when the GenerateHDLTestBench and MultifileTestBench properties are set to

'on'.

TestBenchReferencePostfix — Postfix to reference signal names

'_ref' (default) | character vector | string scalar

Postfix to reference signal names, specified as '_ref',

a character vector, or string scalar. The coder applies this postfix to the

reference output signal in the test bench. The coder represents reference

signal data as arrays.

CONSTANT filter_out_expected : filter_in_data_log_type :=

(

-2.4228738523269194E-03,

-2.0832449820793104E-03,

6.7703446401186345E-03,...SIGNAL filter_out_ref : real := 0.0; -- double ... filter_out_ref <= filter_out_expected(TO_INTEGER(filter_out_addr));

Dependencies

This property applies only when the GenerateHDLTestBench property is set to

'on'.

Clocks and Resets

ClockHighTime — Period during which the test bench drives clock input signals high (1) in ns

5 (default) | positive scalar

Period during which the test bench drives clock input signals high (1) in

ns, specified as 5 or a positive scalar. You can specify

an integer or a double-precision floating-point value with a maximum of 6

significant digits after the decimal point.

Dependencies

This property applies only when the GenerateHDLTestBench and ForceClock

properties are set to 'on'.

ClockLowTime — Period during which the test bench drives clock input signals low (0) in ns

5 (default) | positive scalar

Period during which the test bench drives clock input signals low (0) in

ns, specified as 5 or a positive scalar. You can specify

an integer or a double-precision floating-point value with a maximum of 6

significant digits after the decimal point.

Dependencies

This property applies only when the GenerateHDLTestBench and ForceClock

properties are set to 'on'.

ForceClock — Test bench forces clock input signals

'on' (default) | 'off'

Test bench forces clock input signals, specified as one of these values.

'on'— The test bench forces the clock input signals. The values of theClockHighTimeandClockLowTimeproperties control the clock waveform.'off'— You must drive the clock input signals from an external source.

Dependencies

This property applies only when the GenerateHDLTestBench property is set to

'on'.

ForceClockEnable — Test bench forces clock enable input signals

'on' (default) | 'off'

Test bench forces clock enable input signals, specified as one of these values.

'on'— The test bench forces the clock enable input signals. The polarity is active high (1). This signal also obeys the setting of theHoldTimeproperty.'off'— You must drive the clock enable input signals from an external source.

Dependencies

This property applies only when the GenerateHDLTestBench property is set to

'on'.

TestBenchClockEnableDelay — Clock cycles between deassertion of reset and assertion of clock enable

1 (default) | positive integer

Clock cycles between deassertion of reset and assertion of clock enable,

specified as 1 or a positive integer. The test bench

waits this number of cycles between deasserting the reset signal and

asserting the clock enable signal. The HoldTime

property also applies.

In the figure, the test bench deasserts an active-high reset signal after

the interval labeled Hold Time. The test bench then

asserts clock enable after a further interval, labeled Clock enable

delay.

Dependencies

This property applies only when the GenerateHDLTestBench property is set to

'on'.

ForceReset — Test bench forces the reset input signals

'on' (default) | 'off'

Test bench forces the reset input signals, specified as one of these values.

'on'— The test bench forces the reset input signals. You can also specify a hold time to control the timing of reset by setting theHoldTimeproperty.'off'— You must drive the reset input signals from an external source.

Dependencies

This property applies only when the GenerateHDLTestBench property is set to

'on'.

HoldTime — Hold time for input data values and forced reset signals in ns

2 (default) | positive scalar

Hold time for input data values and forced reset signals in ns, specified

as 2 or a positive scalar. The test bench holds filter

data input signals and forced reset input signals for the specified time

interval past the rising clock edge. You can specify an integer or a

double-precision floating-point value with a maximum of 6 significant digits

after the decimal point.

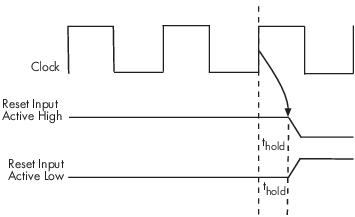

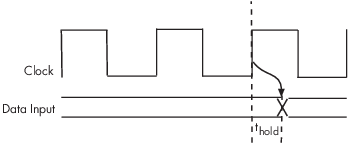

These figures show the application of a hold time,

thold, for reset and data input signals. The

signals are forced to active high and active low. The ResetLength

property is set to 2 cycles, and the test bench asserts the reset signal for

a total of 2 cycles plus thold.

Hold Time for Reset Input Signals

Hold Time for Data Input Signals

Dependencies

This property applies only when the GenerateHDLTestBench and ForceReset

properties are set to 'on'.

ResetLength — Number of clock cycles that the test bench asserts the reset signal

2 (default) | positive integer

Number of clock cycles that the test bench asserts the reset signal,

specified as 2 or a positive integer.

The default test bench asserts an active-high reset signal for 2 clock cycles.

Dependencies

This property applies only when the GenerateHDLTestBench property is set to

'on'.

HoldInputDataBetweenSamples — Test bench holds input data of over-clocked filters in a valid state

'off' (default) | 'on'

Test bench holds input data of over-clocked filters in a valid state,

specified as 'off' or 'on'. Serial

architectures and distributed arithmetic architectures implement internal

clock rates higher than the input rate. In such filter implementations, the

base clock runs N cycles (N >= 2)

for each input sample. This property relates to the number of clock cycles

that the test bench holds the input data in a valid state.

'off'— The test bench holds data values in a valid state for one clock cycle. For the nextN-1cycles, data is in an unknown state (expressed as'X'). Forcing the input data to an unknown state verifies that the generated filter code registers the input data only on the first cycle.'on'— The test bench holds input data values in a valid state acrossNclock cycles.

Dependencies

This property applies only when the GenerateHDLTestBench property is set to

'on'.

InitializeTestBenchInputs — Initialize test bench input

'off' (default) | 'on'

Initialize test bench input, specified as one of these values.

'off'— At the start of the simulation, the test bench drives an unknown state (expressed as'X') to the input ports.'on'— At the start of the simulation, the test bench drives zeros to the input ports.

Dependencies

This property applies only when the GenerateHDLTestBench property is set to

'on'.

Stimulus

TestBenchStimulus — Input stimuli applied to generated filter

{'impulse','step','ramp','chirp','noise'} (default) | cell array of character vectors | string array

Input stimuli applied to generated filter, specified as

{'impulse','step','ramp','chirp','noise'}, a cell

array of character vectors, or a string array. The cell or string array must

be a subset of the default set of stimuli. You can specify combinations of

stimuli in any order. For

example:

generatehdl(filt,'InputDataType',numerictype(1,16,15), ... 'GenerateHDLTestbench','on', ... 'TestBenchStimulus',{'ramp','impulse','noise'})

TestBenchUserStimulus property. When

TestBenchUserStimulus is a nonempty vector, it

takes priority over TestBenchStimulus.

Dependencies

This property applies only when the GenerateHDLTestBench property is set to

'on'.

TestBenchUserStimulus — Custom input stimulus

[] (empty vector) (default) | vector of input data

Custom input stimulus, specified as one of these values.

[](empty vector) — The test bench uses theTestBenchStimulusproperty to generate input data.Vector of input data — The test bench applies this input stimulus to the generated filter. You can specify the vector as a function call returning a vector.

For example, this function call generates a square wave with a sample frequency of 8 bits per second (Fs/8).

Specify this stimulus when callingrepmat([1 1 1 1 0 0 0 0],1,10)

generatehdl.generatehdl(filt,'InputDataType',numerictype(1,16,15), ... 'GenerateHDLTestbench','on', ... 'TestBenchUserStimulus',repmat([1 1 1 1 0 0 0 0],1,10))

Dependencies

This property applies only when the GenerateHDLTestBench property is set to

'on'.

TestBenchCoeffStimulus — Coefficient stimulus for FIR or IIR filters

[] (empty vector) (default) | vector of coefficients (FIR filters only) | cell array of coefficient and scale values (IIR filters only)

Coefficient stimulus for FIR or IIR filters, specified as one of these values.

[](empty vector) — The test bench uses the filter object coefficients and forces the input stimuli. This sequence shows the response to the input stimuli and verifies that the interface writes one set of coefficients into the coefficient memory as expected.Vector of coefficients (FIR filters only) — The filter processes the input stimuli twice: once with the filter object coefficients and once with the coefficient stimulus. The test bench verifies that the interface writes two different sets of coefficients into the coefficient memory. For more details, see Generating a Test Bench for Programmable FIR Coefficients.

Cell array of coefficient and scale values (IIR filters only) — Specify the stimulus as a column vector of scale values and a second-order section (SOS) matrix. The filter processes the input stimuli twice: once with the filter object coefficients and once with the coefficient stimulus. The test bench verifies that the interface writes two different sets of coefficients into the coefficient memory. For more details, see Generating a Test Bench for Programmable IIR Coefficients.

Dependencies

This property applies only when the GenerateHDLTestBench property is set to

'on' and the CoefficientSource property is set to

'ProcessorInterface'.

TestBenchFracDelayStimulus — Fractional delay stimulus for single-rate Farrow filters

constant numeric value (default) | vector of numeric values | 'RandSweep' | 'RampSweep'

Fractional delay stimulus for single-rate Farrow filters, specified as one of these values.

Constant numeric value— The test bench drives the fractional delay input signal with a constant value obtained from the filter object.

Vector of numeric values — The test bench drives the fractional delay input signal from this vector. You can specify the vector as a function call returning a vector. The vector must be of the same length as the test bench input signal.

'RandSweep'— The test bench drives the fractional delay input signal by using a vector of values incrementally increasing over the range from 0 to 1. This stimulus signal has the same duration as the input signal to the filter, but changes at a slower rate. Each fractional delay value obtained from the vector is held for 10% of the total duration of the input signal.'RampSweep'— The test bench drives the fractional delay input signal by using a vector of random values from 0 through 1. This stimulus signal has the same duration as the input signal to the filter, but it changes at a slower rate. Each fractional delay value obtained from the vector is held for 10% of the total duration of the input signal.

See Code Generation Properties for Farrow Filters.

Dependencies

This property applies only when the GenerateHDLTestBench property is set to

'on'.

TestBenchRateStimulus — Rate input stimulus for CIC filters

maximum rate change factor (default) | integer

Rate input stimulus for Cascaded Integrator-Comb (CIC) filters, specified

as the maximum rate change factor or an integer. If you do not specify

TestBenchRateStimulus, the coder assumes that the

filter is designed with the maximum rate expected. The decimation factor

(for CIC decimators) or interpolation factor (for CIC interpolators) is set

to this maximum rate-change factor.

See Variable Rate CIC Filters.

Dependencies

This property applies only to variable-rate CIC filters, when the

GenerateHDLTestBench and AddRatePort properties are set to

'on'.

Cosimulation

GenerateCosimBlock — Generate Simulink® model of HDL Cosimulation blocks

'off' (default) | 'on'

Generate Simulink model of HDL Cosimulation blocks, specified as

'off' or 'on'. The generated

Simulink model contains two HDL Cosimulation blocks: one for

Siemens®

ModelSim™ and one for Cadence Incisive®. The coder configures these blocks to conform to the port and

data type interface of the selected filter. Use these blocks to cosimulate

your design with the desired HDL simulator in Simulink.

Dependencies

This feature requires an HDL Verifier™ license.

GenerateCosimModel — Generate Simulink model of realized filter and HDL Cosimulation block

'none' (default) | 'ModelSim' | 'Incisive'

Generate Simulink model of realized filter and HDL Cosimulation block, specified

as 'none', 'ModelSim', or

'Incisive'. When you set this property to

'ModelSim' or 'Incisive', the

coder generates and opens a Simulink model. The model contains an HDL cosimulation block for the

selected simulator, and a behavioral implementation of the filter design.

The model applies generated input stimuli and compares the output of the EDA

simulator with the output of the behavioral filter subsystem. You can

customize the input stimulus and error margin using the same properties as

you would for the generated HDL test bench.

See Generating a Simulink Model for Cosimulation with an HDL Simulator.

Dependencies

This feature requires an HDL Verifier license.

Tips

If you use the function fdhdltool to generate HDL code, you can

set the corresponding properties on the Test Bench tab in the

Generate HDL tool.

Version History

Introduced before R2006a

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

Select a Web Site

Choose a web site to get translated content where available and see local events and offers. Based on your location, we recommend that you select: .

You can also select a web site from the following list

How to Get Best Site Performance

Select the China site (in Chinese or English) for best site performance. Other MathWorks country sites are not optimized for visits from your location.

Americas

- América Latina (Español)

- Canada (English)

- United States (English)

Europe

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)

Asia Pacific

- Australia (English)

- India (English)

- New Zealand (English)

- 中国

- 日本Japanese (日本語)

- 한국Korean (한국어)