Increment Real World

Increase real-world value of signal by one

Libraries:

Simulink /

Additional Math & Discrete /

Additional Math: Increment - Decrement

HDL Coder /

Math Operations

Description

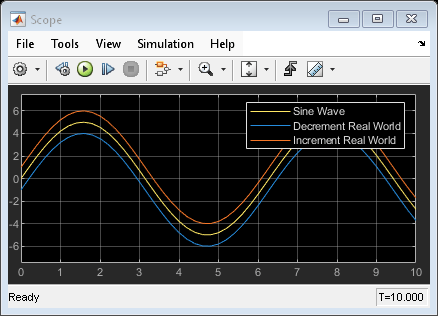

The Increment Real World block increases the real-world value of the signal by one.

Overflows always wrap.

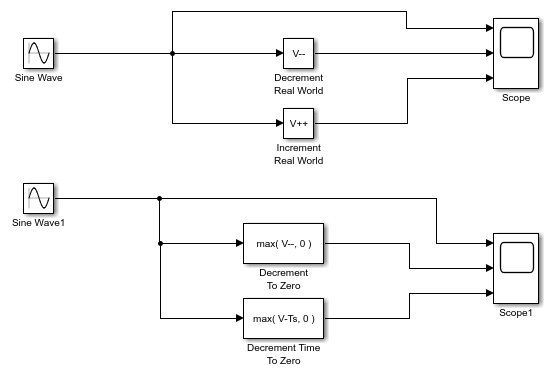

Examples

Ports

Input

Output

Block Characteristics

Data Types |

|

Direct Feedthrough |

|

Multidimensional Signals |

|

Variable-Size Signals |

|

Zero-Crossing Detection |

|