使用信号记录保存信号数据

可以使用信号记录从仿真中捕获信号数据,而无需向模型中添加模块。当信号标记为记录时,软件会显示记录标记  。此示例说明如何使用信号记录将仿真数据记录到工作区和仿真数据检查器中。

。此示例说明如何使用信号记录将仿真数据记录到工作区和仿真数据检查器中。

要收集和使用信号记录数据,请执行以下步骤:

您也可以记录一部分标记信号。若要在开发模型时测试模型的各个部分,有一种方法是标记要记录的信号的超集,然后覆盖信号记录设置,选择要记录的信号的不同子集。您可以使用信号记录选择器或编程接口。有关详细信息,请参阅Override Signal Logging Settings。

有关捕获仿真信号数据的其他方法的摘要,请参阅保存仿真数据。

注意

保存具有标记为记录的信号的自定义库模块可能会导致记录不必要的数据,因此不推荐这样做。请改为在模型中放置没有记录的信号的自定义库模块。然后,标记只针对该库模块实例进行记录的信号。

由于不推荐在自定义库内记录信号,因此在仿真选项卡上,记录信号按钮被禁用。要标记在自定义库内记录的信号,请点击该信号,将鼠标暂停在三个点上,然后点击记录所选信号。

打开模型

此示例使用由以下方程给出的阻尼非线性弹簧的模型

,

其中:

a = 3 米是弹簧的静止长度。

k = 1 牛/米是弹簧常数。

该模型不包含任何输出端口模块,也没有标记为记录的信号。此示例说明如何启用信号记录并指定信号记录名称。

为模型启用信号记录

默认情况下,信号记录处于启用状态。启用信号记录后,软件会在仿真期间记录您标记为记录的信号的数据。您可以使用“配置参数”对话框来启用或禁用模型的信号记录。例如,检查是否对模型 damped_nonlin_spring 启用了信号记录。

在建模窗格中,选择模型设置。

在数据导入/导出选项卡中,确保信号记录参数处于选中状态。

信号记录已启用,因此当您在模型中标记要记录的信号时,软件会在仿真期间记录信号数据。如果未选择信号记录参数,则软件不会记录标记为信号记录的信号。

您还可以使用 set_param 函数以编程方式启用或禁用模型的信号记录。

set_param("damped_nonlin_spring",'SignalLogging','on')

标记要记录的信号

为了分析阻尼非线性弹簧动态特性,请标记要记录的信号。来自名为 Integrator1 的 Integrator 模块的信号表示位置。来自名为 Integrator 的 Integrator 模块的信号表示速度。要记录弹簧的位置和速度的信号数据,请标记要记录的信号:

选择模型中的信号。

在仿真选项卡上,点击记录信号。

记录标记  表示信号被标记为进行信号记录。

表示信号被标记为进行信号记录。

您也可以使用 Simulink.sdi.markSignalForStreaming 函数以编程方式标记要记录的信号。

Simulink.sdi.markSignalForStreaming('damped_nonlin_spring/Integrator',1,'on') Simulink.sdi.markSignalForStreaming('damped_nonlin_spring/Integrator1',1,'on')

您可以使用模型数据编辑器来简化标记信号的过程,以便在整个模型层次结构中进行信号记录。模型数据编辑器显示模型中信号的扁平列表,您可以对其进行排序、分组和过滤。

指定信号名称

damped_nonlin_spring 模型中的信号是未命名的。通过对在模型中记录的信号进行命名,您可以更轻松地分析记录数据。默认情况下,软件使用工作区和仿真数据检查器中的信号名称。如果信号没有名称,则在将数据记录到工作区时,软件将使用空白名称。仿真数据检查器按模块路径和端口号识别未命名的信号。

例如,为了使记录的数据更容易分析,您可以通过交互方式命名表示位置和速度的信号。

双击名为

Integrator1的模块的信号输出。然后,键入position。双击名为

Integrator的模块的信号输出。然后,键入velocity。

您也可以通过编程方式指定信号名称。

获取表示位置的信号和表示速度的信号的端口句柄。

posph = get_param('damped_nonlin_spring/Integrator1','PortHandles'); velph = get_param('damped_nonlin_spring/Integrator','PortHandles');

使用

get_param函数获取连接到每个端口的信号线的句柄。poslh = get_param(posph.Outport,'Line'); vellh = get_param(velph.Outport,'Line');

使用

set_param函数设置信号名称。set_param(poslh,'Name','position') set_param(vellh,'Name','velocity')

您还可以指定不同于模型中使用的信号名称的信号记录名称。对于您要在模型中保持未命名的信号,或与模型层次结构中的另一个信号重名的信号,指定信号级记录名称非常有用。要设置自定义信号记录名称,您可以使用信号属性对话框、插桩属性对话框或模型资源管理器。

仿真模型并查看数据

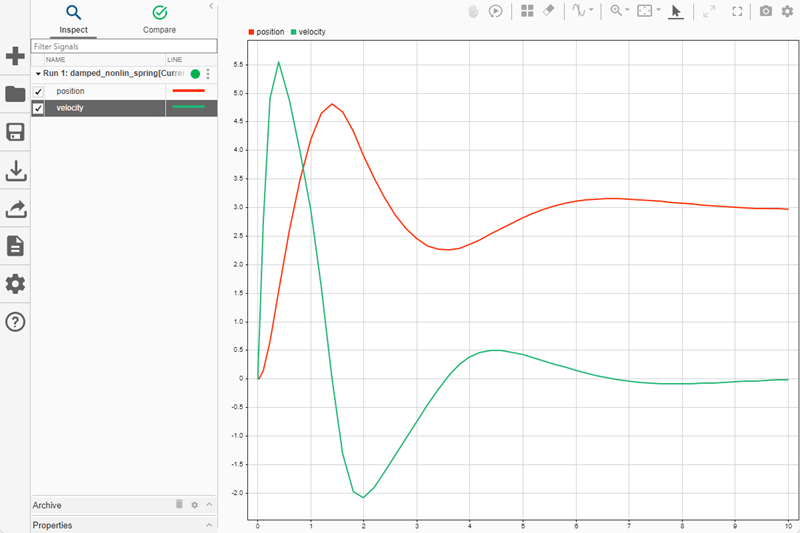

由于信号记录将数据记录到仿真数据检查器,您可以轻松地可视化仿真数据。要在仿真数据检查器中查看记录的位置和速度数据,请执行以下操作:

对模型进行仿真。

在仿真选项卡的查看结果下,点击数据检查器。

在仿真数据检查器中,选择

position和velocity信号以将信号数据添加到绘图区域。

最初,弹簧处于压缩状态。松开时,弹簧会振荡。最终,由于系统阻尼,弹簧在其静止弹簧长度 3 米处停止。

有关在仿真数据检查器中查看记录的信号数据的详细信息,请参阅Inspect Simulation Data和Create Plots Using the Simulation Data Inspector。

以编程方式访问信号记录数据

您还可以使用 MATLAB® 来分析记录的工作区数据。默认情况下,所有记录的仿真数据都以名为 out 的变量中的单个 Simulink.SimulationOutput 对象形式返回。

out

out =

Simulink.SimulationOutput:

logsout: [1x1 Simulink.SimulationData.Dataset]

tout: [59x1 double]

SimulationMetadata: [1x1 Simulink.SimulationMetadata]

ErrorMessage: [0x0 char] 信号记录数据将分组到 Simulink.SimulationData.Dataset 对象中,默认名称为 logsout。当仿真结果以单个 Simulink.SimulationOutput 对象形式返回时,您可以使用圆点来访问信号记录数据。

out.logsout

ans =

Simulink.SimulationData.Dataset 'logsout' with 2 elements

Name BlockPath

________ ________________________________

1 [1x1 Signal] velocity damped_nonlin_spring/Integrator

2 [1x1 Signal] position damped_nonlin_spring/Integrator1

- Use braces { } to access, modify, or add elements using index.当您将数据记录到工作区并返回单个仿真输出时,Simulink.SimulationOutput 对象包含的每个属性都对应于一个记录类型。例如,当您使用信号记录来记录数据并使用 Dataset 对象的默认工作区变量名称时,Simulink.SimulationOutput 对象具有属性 logsout,该属性包含记录的信号数据。您可以使用“配置参数”对话框来启用或禁用单一仿真输出参数。有关示例,请参阅访问 Simulink.SimulationOutput 对象中的数据。

使用信号记录功能记录的每个信号都存储为 Dataset 对象中的一个元素。要更改信号记录 Dataset 对象的工作区变量名称,您可以使用“配置参数”对话框中信号记录参数旁边的文本框。