为依赖关系分析细化死逻辑

要为依赖关系分析细化模型中的死逻辑,请使用模型切片器。为提供精确的切片,模型切片器利用 Simulink® Design Verifier™ 死逻辑分析来删除模型中所有不可达的路径。模型切片器会识别死逻辑,并为依赖关系分析细化模型切片。有关死逻辑的详细信息,请参阅死逻辑检测 (Simulink Design Verifier)。

分析死逻辑

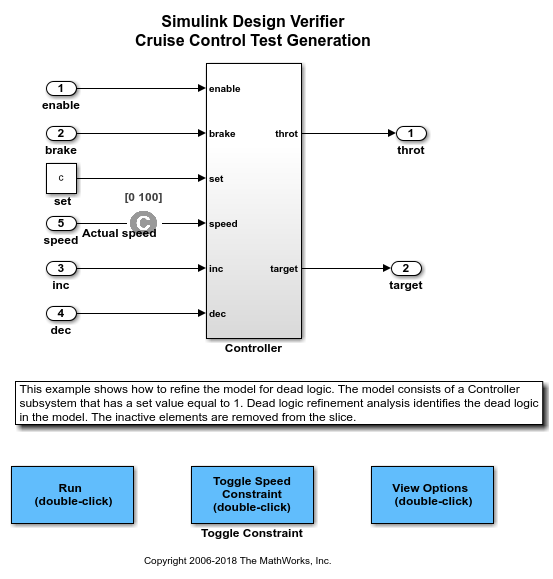

此示例说明如何细化模型中的死逻辑。sldvSlicerdemo_dead_logic 模型包含死逻辑路径,需细化后方可执行依赖关系分析。

1.打开 sldvSlicerdemo_dead_logic 模型。

2.在 App 选项卡的模型验证、确认和测试库下,点击模型切片器。

open_system('sldvSlicerdemo_dead_logic');

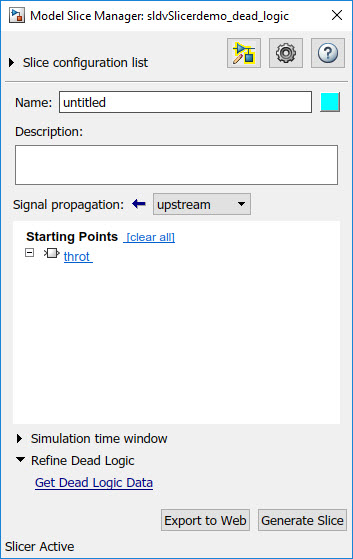

打开 Controller 子系统,并将 throt 输出端口添加为起点。

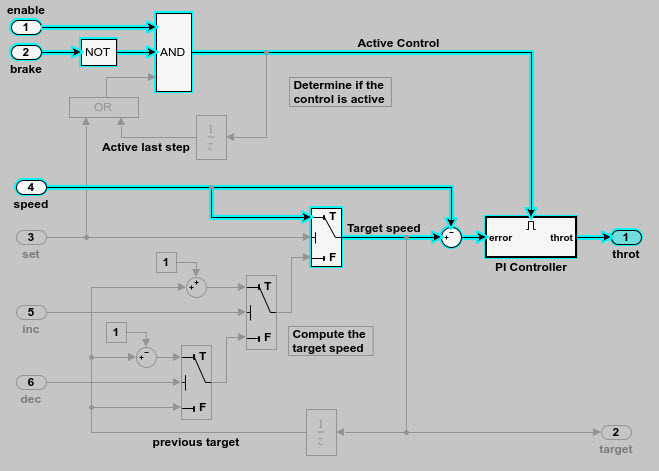

模型切片器会突出显示 throt 输出端口的上游依赖项。

2.在模型切片管理器中,选择细化死逻辑。

3.点击获取死逻辑数据。

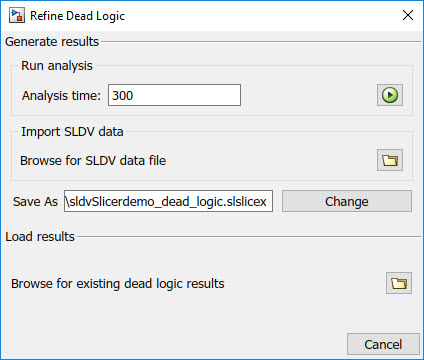

4.指定分析时间并运行分析。您可以从 sldvData 文件中导入现有的死逻辑结果或加载现有的 .slslicex 数据以进行分析。有关详细信息,请参阅Refine Highlighted Model by Using Existing .slslicex or Dead Logic Results。

由于 set 输入等于 true,因此为依赖关系分析删除了开关的 False 输入。类似地,模块 OR 的输出始终为 true,因此被从模型切片中删除。