对模型执行分析

关于此示例

以下部分描述了一个示例模型 sldvdemo_cruise_control。本示例说明如何使用 Simulink® Design Verifier™ 生成实现完整模型覆盖率的测试用例。通过这个示例,您将学会如何使用 Simulink Design Verifier 分析模型并解释结果。

打开模型

要打开 sldvdemo_cruise_control 模型,请在 MATLAB® 提示符下输入:

openExample('sldv/CruiseControlTestGenerationExample',... 'supportingFile', 'sldvdemo_cruise_control');

生成测试用例

运行分析

要为 sldvdemo_cruise_control 模型生成测试用例,点击生成测试。

Simulink Design Verifier 开始分析模型以生成测试用例,并打开 Simulink Design Verifier 结果摘要窗口。“结果摘要”窗口显示显示分析进度的运行日志。

如果您需要在分析运行时终止分析,点击停止。软件会询问您是否想要产生结果。如果您点击是,软件将根据迄今为止获得的结果创建一个数据文件。数据文件的路径名出现在“结果摘要”窗口中。

数据文件是一个包含名为 sldvData 的结构体的 MAT 文件。该结构体存储软件在分析过程中收集和产生的数据。

有关详细信息,请参阅 管理 Simulink Design Verifier 数据文件。

生成分析结果

当 Simulink Design Verifier 完成对 sldvdemo_cruise_control 模型的分析时,“结果摘要”窗口会显示几个选项。下面列出了其中一些:

在模型上突出显示分析结果

详细分析报告:(HTML) (PDF)

创建框架模型

仿真测试并生成模型覆盖率报告

将测试用例/反例保存到电子表格中

注意

当您分析其他模型时,根据分析结果,您可能会看到一个选项子集。

以下部分详细描述了这些选项。

在模型上突出显示分析结果

在 Simulink Design Verifier 结果摘要窗口中,如果点击在模型上突出显示分析结果,软件将根据分析结果以三种不同的颜色突出显示模型中的对象:

当您突出显示模型上的分析结果时,Simulink Design Verifier 结果检查器将打开。当您点击模型中具有分析结果的对象时,结果检查器将显示该对象的结果摘要。

绿色:满足的目标. 绿色轮廓表示分析针对该模块的所有目标生成了测试用例。如果该模块是子系统或 Stateflow® 原子子图,则绿色轮廓表示分析为与子对象相关的所有目标生成了测试用例。

例如,在 sldvdemo_cruise_control 模型中,绿色轮廓表示 PI 控制器子系统满足所有测试目标。结果检查器列出了 PI 控制器子系统的两个满足的测试目标。

橙色:目标未决. 橙色轮廓表示分析无法确定目标是否可满足。这种情况可能发生在以下情况:

分析超时

该软件无需生成测试用例即可满足测试目标,因为:

自动插桩错误

分析引擎的局限性

红色:目标无法满足. 红色轮廓表示分析发现了一些无法生成测试用例的目标,很可能是由于模型中无法访问的设计元素。

在下面的例子中,输入 2 始终满足 Switch 模块的标准,因此 Switch 模块永远不会通过输入 3 的值。

详细分析报告:(HTML) (PDF)

在 Simulink Design Verifier 结果摘要窗口中,如果您点击 HTML 上的详细分析报告:(HTML) (PDF),软件保存然后打开分析的详细报告。报告的路径是:

<current_folder>/sldv_output/...

sldvdemo_cruise_control/sldvdemo_cruise_control_report.htmlHTML 报告包括以下章节。

有关每个报告章节的描述,请参阅:

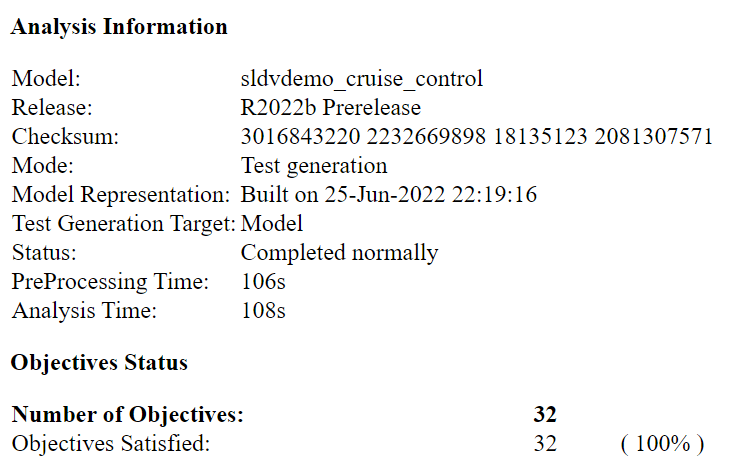

摘要. 在目录中,点击摘要以显示摘要章节,其中包含分析信息子部分下的以下信息:

模型名称

发布和校验和信息

分析模式(测试生成、属性证明、设计错误检测)

分析状态

分析时长(秒)

摘要下的目标状态子部分显示已满足的目标数量。

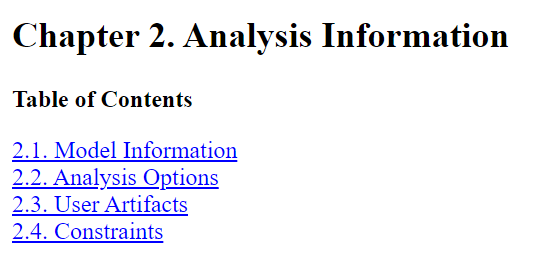

分析信息. 在目录中,点击分析信息以显示有关所分析模型和分析选项的信息。您可以点击其中任意一个选项来了解有关模型分析的更多信息。

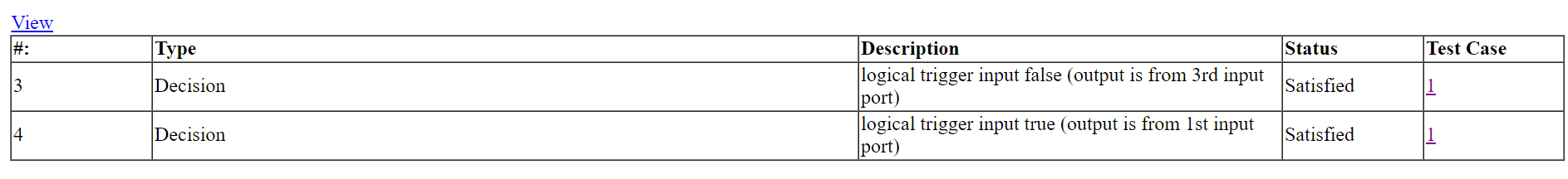

测试目标状态. 在目录中,点击测试目标状态以显示满足的目标表。下图显示了 sldvdemo_cruise_control 模型中满足的部分目标列表。

目标状态

满足的目标表列出了该模型的以下信息:

# - 目标编号

类型 - 目标类型

模型项目 - 模型中用于测试目标的元素。点击此链接可以显示突出显示此元素的模型。

描述 - 目标描述

测试用例 - 实现目标的测试用例。点击此链接可获取有关该测试用例的更多信息。

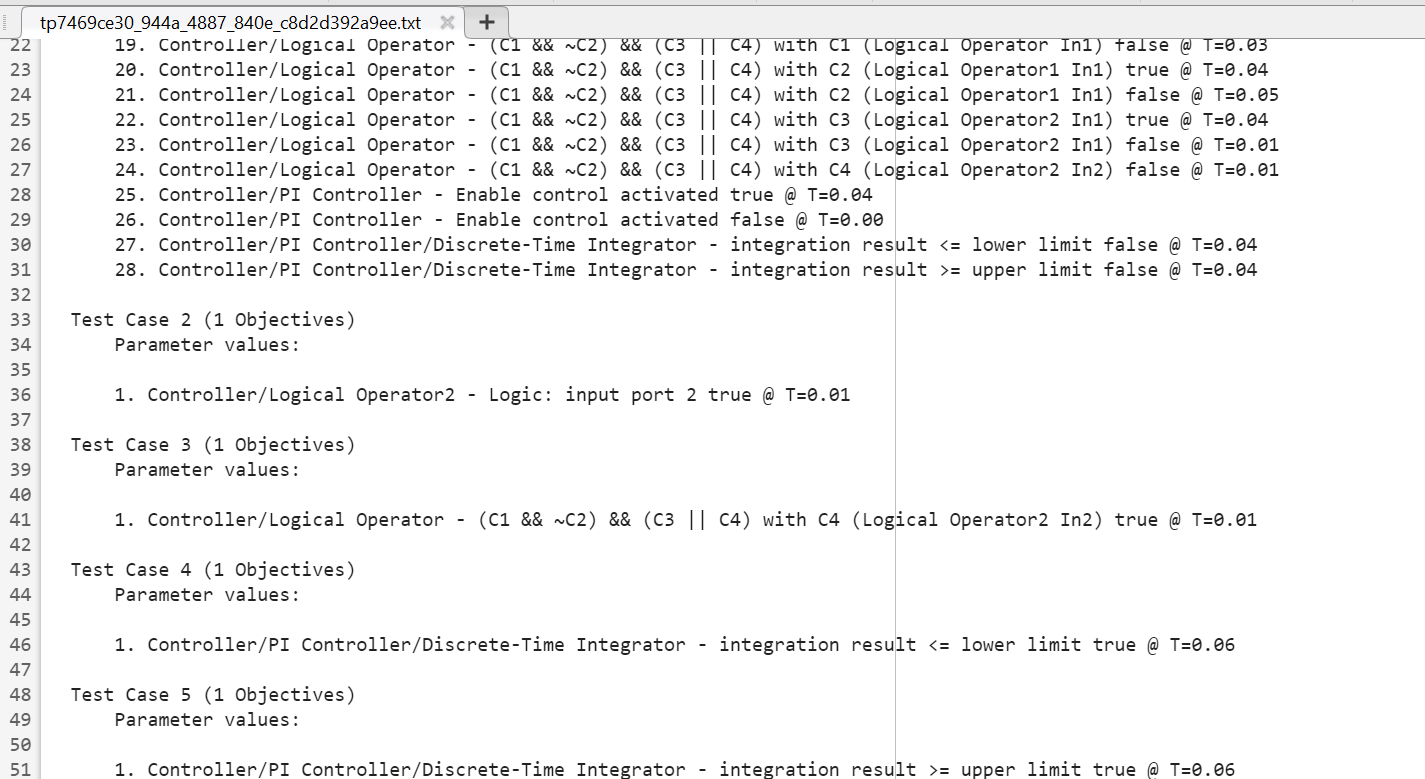

在目标 32 的行中,点击测试用例编号 (5) 以显示有关报告的测试用例章节中测试用例 5 的更多信息。

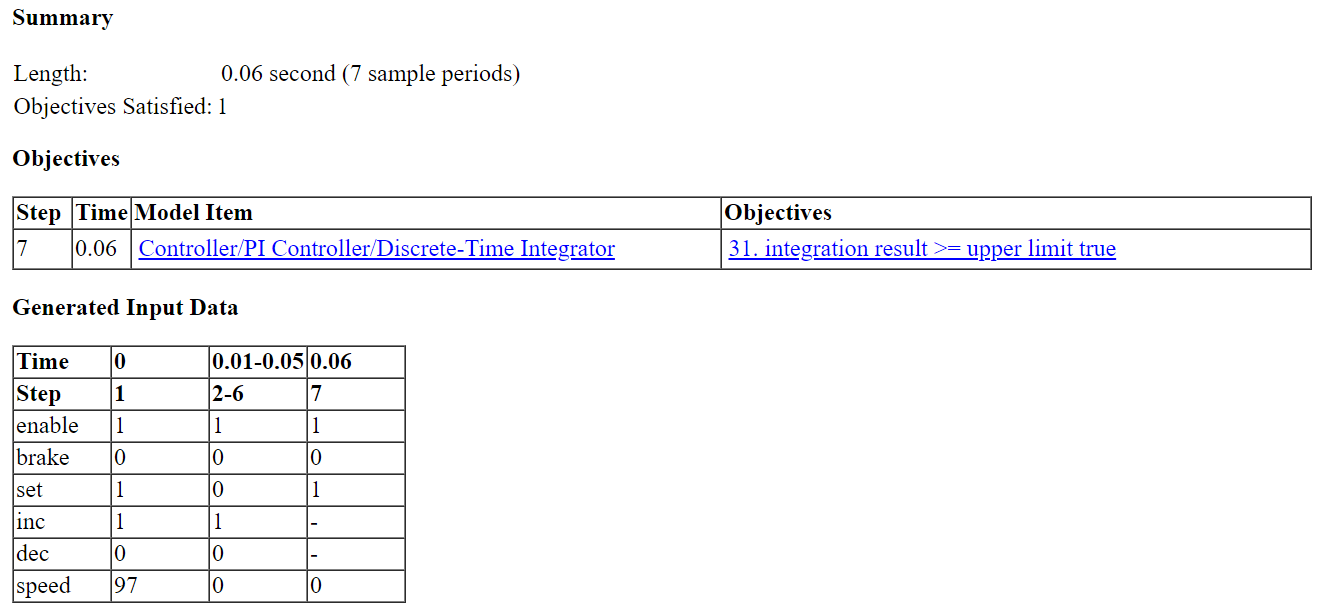

测试用例 5

在这个例子中,测试用例 5 满足一个目标,即积分结果大于或等于 Discrete-Time Integrator 模块中的上限 T。表格列出了从时间 0 到时间 0.06 的六个信号的值。

模型项目. 在目录中,点击模型项目以查看定义覆盖率目标的模型中每个项目的详细信息。该表包括分析结束时目标的状态。点击表中的链接可查看有关满足目标的详细信息。

模型项 - 控制器/开关 3

模型项 - 控制器/开关 2

测试用例. 在目录中点击测试用例可以显示每个生成的测试用例的详细信息,包括:

执行测试用例的时间长度

已达成目标的数量

关于已实现目标的详细信息

输入数据

创建框架模型

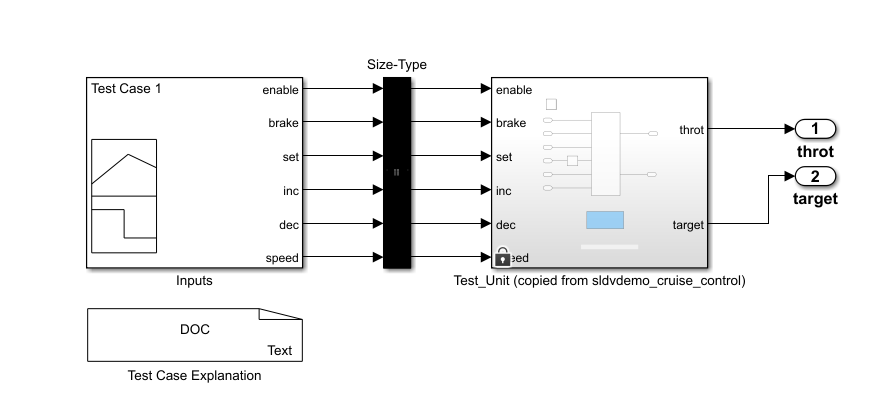

在 Simulink Design Verifier 结果摘要窗口中,如果点击创建框架模型,软件将创建并打开一个名为 sldvdemo_cruise_control_harness 的框架模型。

框架模型包含以下模块:

Test Case Explanation模块是 DocBlock 模块,用于记录生成的测试用例。双击Test Case Explanation查看每个测试用例所满足的测试用例目标的描述。

Test Unit模块是 Subsystem 模块,其中包含软件分析的原始模型的副本。双击Test Unit模块查看其内容,确认它是sldvdemo_cruise_control模型的副本。注意

您可以配置框架模型以使用 Model 模块而不是使用子系统来引用您正在分析的模型。在“配置参数”对话框的 Design Verifier > 结果窗格中,选择分析后生成单独的框架模型和生成的框架中的引用输入模型。

Inputs模块是包含生成的测试用例信号的 Signal Editor 模块。双击Inputs模块打开信号编辑器对话框并查看八个测试用例信号。Size-Type模块是一个将信号从Inputs模块传输到Test Unit模块的子系统。该模块验证信号的大小和数据类型是否与 Test Unit 模块一致。

Inputs 模块的模块参数对话框包含三个测试用例。

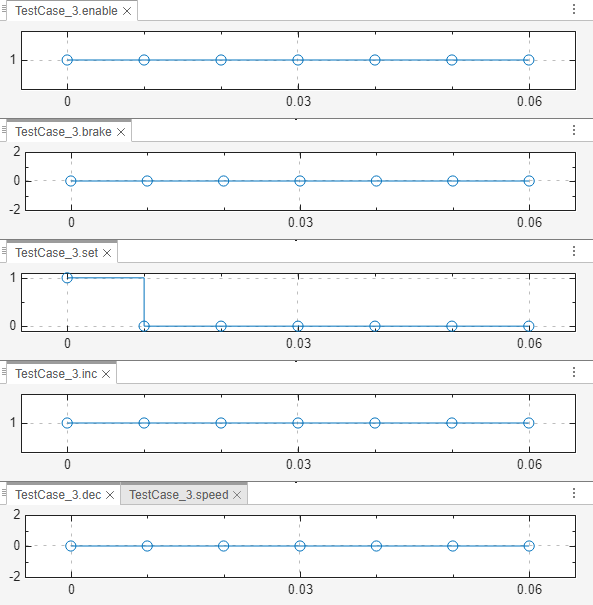

要查看测试用例 3,请从激活场景列表中选择 TestCase_3,然后点击打开信号编辑器按钮

以打开信号编辑器。

以打开信号编辑器。在测试用例 3 中,0.01 秒时:

enable和inc信号保持为 1。brake和dec信号保持为 0。set信号从 1 变为 0。speed信号从 100 变为 0。

在

Inputs模块中,信号组满足Test Case Explanation模块中描述的测试目标。为了确认 Simulink Design Verifier 实现了完整的模型覆盖率,请使用所有测试用例来仿真框架模型。在框架模型的工具条中,点击全部运行(覆盖率)。

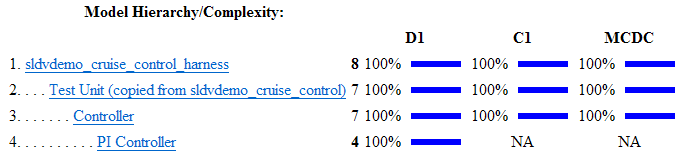

Simulink 软件仿真了所有测试用例。Simulink Coverage™ 软件收集框架模型的覆盖率数据并显示覆盖率报告。报告摘要显示,

sldvdemo_cruise_control_harness模型实现了 100%的覆盖率。摘要

仿真测试并生成模型覆盖率报告

在 Simulink Design Verifier 结果摘要窗口中,如果点击仿真测试并生成模型覆盖率报告,软件将仿真模型并为 sldvdemo_cruise_control 模型生成覆盖率报告。该软件使用以下路径和文件名存储报告:

current_folder/sldv_output/sldvdemo_cruise_control/... sldvdemo_cruise_control_report.html

当您点击全部运行并得出覆盖率以在框架模型中仿真测试时,您可能会看到此覆盖率报告与您为模型本身生成的报告之间的差异:

框架模型覆盖率报告可能包含额外的时间步。当您收集框架模型的覆盖率时,模型停止时间等于最长测试用例的停止时间。因此,当您仿真较短的测试用例时,您可能会获得额外的覆盖率。

由于框架模型的结构体,框架模型中测试单元子系统的圈复杂度覆盖率可能与模型本身的覆盖率不同。

将测试用例/反例保存到电子表格中

如果您希望将生成的测试用例或反例保存在电子表格中,点击 Simulink Design Verifier 结果摘要窗口中的将测试用例/反例保存到电子表格中。

合并测试用例

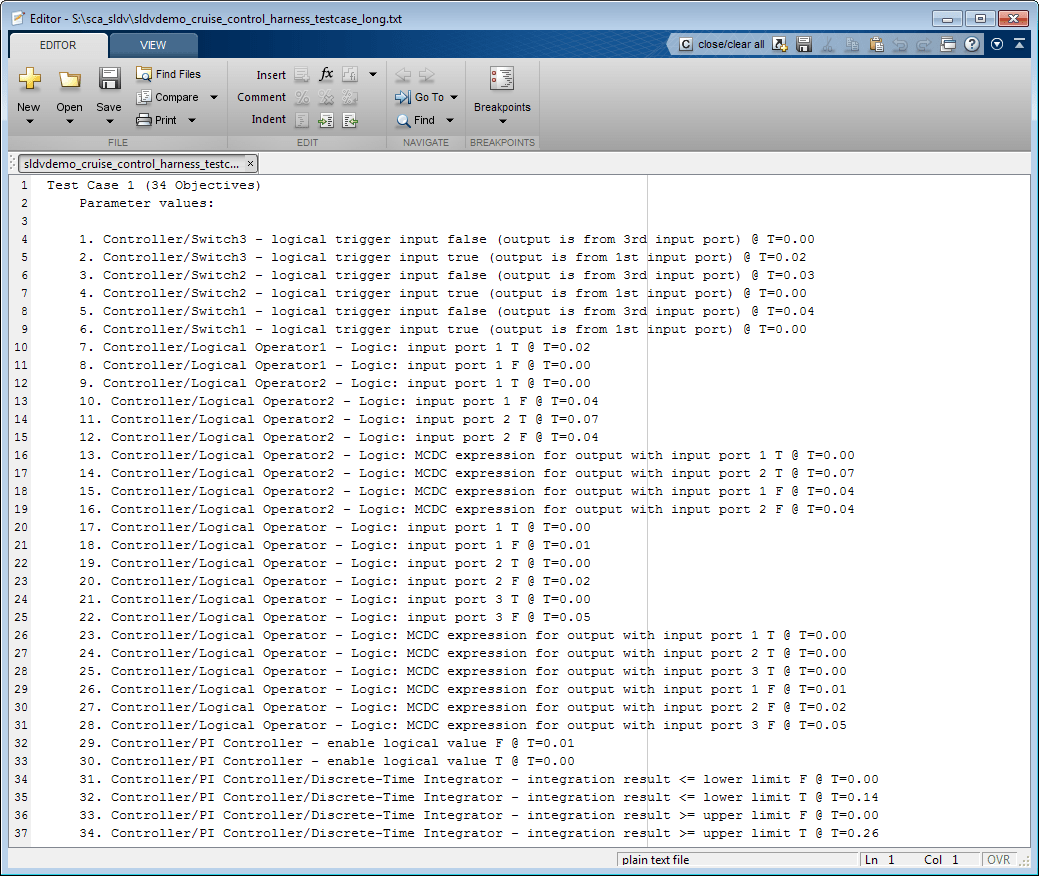

如果您希望查看合并为较少数量测试用例的结果,请将测试套件优化参数设置为 LongTestcases。当您使用 LongTestcases 优化时,分析会生成更少但更长的测试用例,每个测试用例都能满足多个测试目标。

打开 sldvdemo_cruise_control 模型并使用 LongTestcases 优化重新运行分析:

在 Design Verifier 选项卡的准备部分中,从模式设置的下拉菜单中点击设置。

在配置参数对话框的 Design Verifier 窗格下,选择测试生成,将测试套件优化参数设置为 LongTestcases。点击应用,然后点击确定关闭配置参数对话框。

在

sldvdemo_cruise_control模型中,点击生成测试。在结果摘要窗口中,点击创建框架模型。

在框架模型中,

Inputs模块和Test Case Explanation模块现在包含一个较长的测试用例,而不是之前创建的八个较短的测试用例。

点击全部运行并得出覆盖率来收集覆盖率。

分析仍然满足全部 34 个目标。