死逻辑分析结果解析

此示例演示如何使用 sldvexCommonCausesOfDeadLogic 模型隔离死逻辑的潜在原因。死逻辑检测在模型中查找导致模型元素保持非活动状态的不可达目标。

工作流

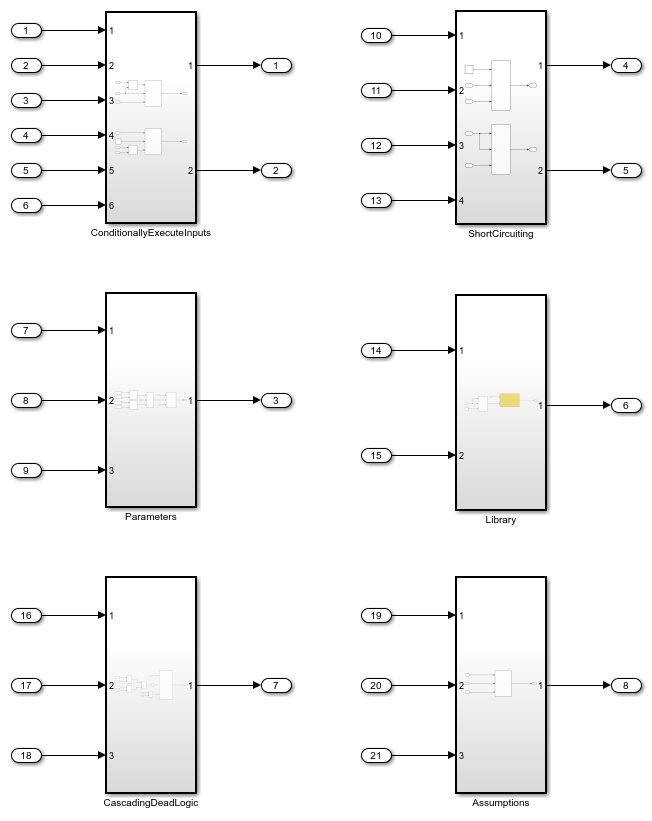

sldvexCommonCausesOfDeadLogic 模型演示了一些导致模型中出现死逻辑的常见模式。该模型中的六个子系统分别表示不同的模式。这些子系统是:

子系统的条件执行

分析过程中 Logical Operator 模块的短路

参数值被视为常量

库链接模块

上游模块

对信号范围的限制

运行死逻辑分析

按照以下步骤运行死逻辑分析:

1.打开模型 sldvexCommonCausesOfDeadLogic。

open_system('sldvexCommonCausesOfDeadLogic');

2.在 App 窗格中,打开 Design Verifier。

3.在 Design Verifier 选项卡上,点击错误检测设置。

4.在配置参数对话框中:

a.启用死逻辑(部分) 选项。

b.清除运行穷举分析选项(如果已选中)。

c.将要分析的覆盖率目标设置为条件决策选项。下拉菜单中的可用选项包括决策、条件决策和 MCDC。

5.在 Design Verifier 选项卡中,点击检测设计错误。

分析并查看结果

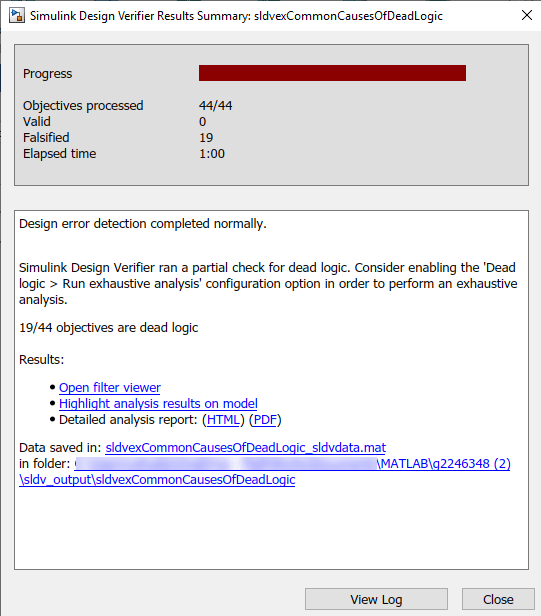

软件会分析模型以检测死逻辑,并在“结果摘要”窗口中显示结果。结果表明,44 个目标中有 19 个是死逻辑。

在子系统模块中突出显示分析结果

本节介绍导致 sldvexCommonCausesOfDeadLogic 模型中出现死逻辑的常见模式。在“结果摘要”窗口中,点击在模型上突出显示分析结果。存在死逻辑的子系统会以红色突出显示。这些子系统是:

ConditionallyExecuteInputs

ShortCircuiting

Parameters

Library

CascadingDeadLogic

ConditionGreaterThan0

sldvexCommonCausesOfDeadLogic 模型中的子系统介绍了这些模式。每个以红色突出显示的子系统模块都存在死逻辑。我们来逐一考虑每个子系统,以分析并突出显示结果。

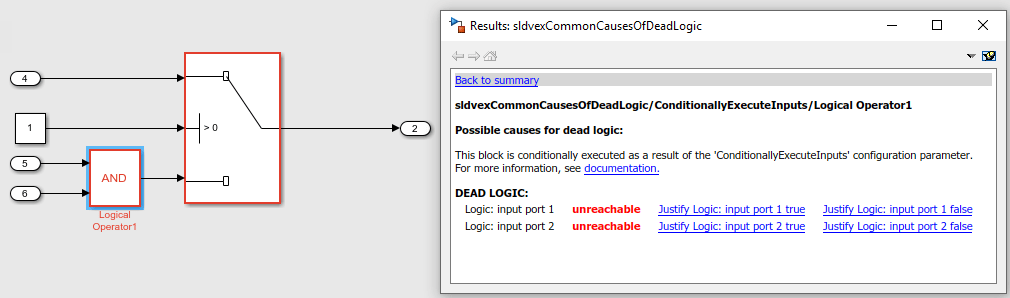

1.子系统的条件执行

如果您的模型包含 Switch 或 Multiport Switch 模块,并且“条件输入分支执行”参数设置为 On,则条件执行通常会导致意外的死逻辑。打开 ConditionallyExecuteInputs 子系统,然后点击以红色突出显示的 AND 模块。“结果”窗口会汇总死逻辑的相关信息。

在该子系统中,“条件输入分支执行”参数设置为 On。AND Logical Operator 模块基于条件执行,这会导致该子系统出现死逻辑。

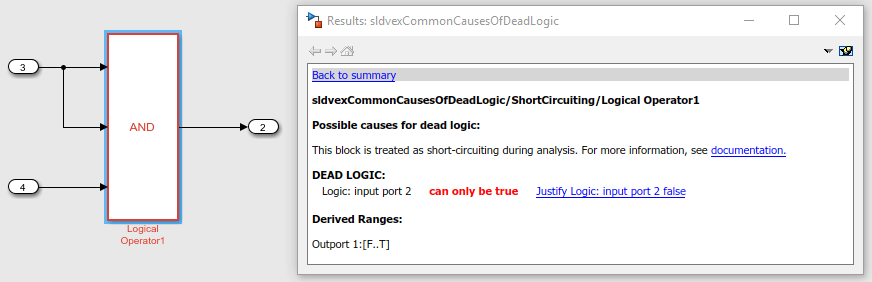

2.分析过程中 Logical Operator 模块的短路

Simulink Design Verifier 在分析死逻辑时会将逻辑模块视为具有短路特性。打开 ShortCircuiting 子系统,然后点击以红色突出显示的 AND 模块。“结果”窗口会汇总死逻辑的相关信息。

在此模型中,如果 In3 为 false,软件会由于短路而忽略第三个输入。“结果”窗口中将此作为死逻辑的潜在解释。

3.参数值被视为常量

如果您的模型包含参数,Simulink Design Verifier 会默认将这些参数值视为常量,这可能导致模型中出现死逻辑。在这些情况下,可考虑将这些参数配置为在分析过程中可调整。打开 ShortCircuiting 子系统,然后点击以红色突出显示的 Switch 模块。“结果”窗口会汇总死逻辑的相关信息。

在本例中,所有参数都设置为零。这导致 Less Than 模块出现死逻辑。

4.库链接模块

ProtectedDivide 库子系统具有除以零保护机制。库模块中可能包含一些防御性条件,这些条件在某些使用这些模块的位置是多余的。在某些情况下,这可能会导致死逻辑。打开库模块,然后点击以红色突出显示的 ProtectedDivide 子系统。在本例中,ProtectedDivide 库子系统的输入永远不会出现除以零错误。这导致保护逻辑成为死逻辑。Equal 模块显示该死逻辑。“结果”窗口会汇总死逻辑的相关信息。

可考虑对这些库模块产生的死逻辑进行申述。

5.上游模块

当某个特定模块出现死逻辑时,通常会导致级联效应,从而使得下游模块也出现死逻辑。打开 CascadingDeadLogic 子系统,然后点击以红色突出显示的 Less Than 模块。“结果”窗口会汇总死逻辑的相关信息。

Less Than 模块中的死逻辑导致相应下游模块中也出现死逻辑。因此,在检查任何下游死逻辑之前检查上游死逻辑通常会很有帮助。

6.对信号范围的限制

在测试生成中,具有最小值和最大值约束的根级 Inport 模块以及 Test Condition 模块可能会导致死逻辑。例如,假设有 ConditionGreaterThan0 Switch 模块,其中第二个 Inport 模块的最小值和最大值范围分别为 1 和 100。这会导致该子系统中的 Switch 模块出现死逻辑,因为这个有约束的范围意味着信号将始终大于 0。

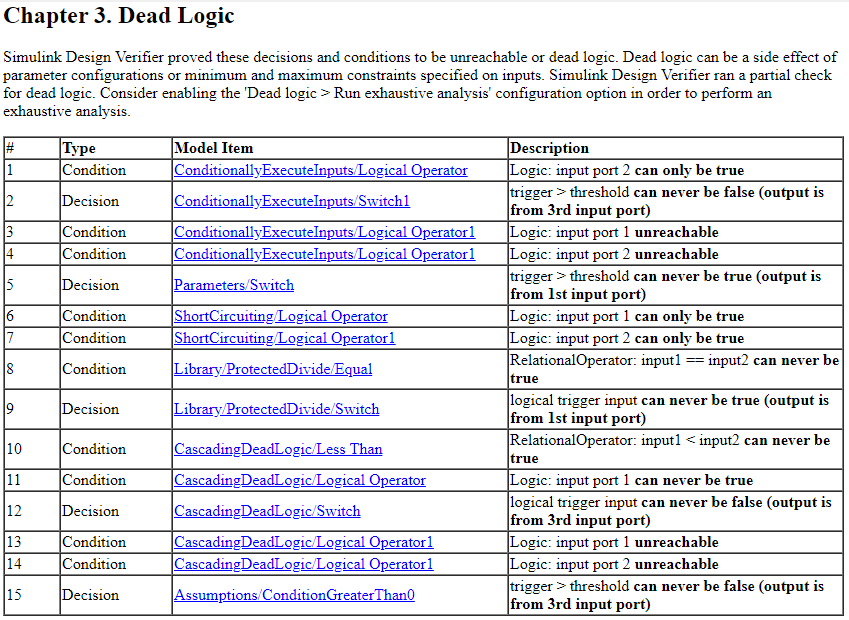

查看分析报告

在“结果摘要”窗口中,点击 HTML 可查看详细的分析报告。报告汇总了模型中所有死逻辑的分析结果。

要执行死逻辑的穷举分析,请在配置参数窗口的设计错误检测窗格中,选择运行穷举分析。软件会将详细分析结果存储在 Simulink Design Verifier 数据文件的 DeadLogic field 中。您可以使用数据文件进一步分析结果。

注意:缺陷检查器会自动调用死逻辑、越界数组访问、除以零、整数溢出以及指定的最小值和最大值违规检查。要指定检查,请将缺陷检查器设置为 off。

使用模型切片器查找影响模块的参数

您可以按照以下步骤使用模型切片器来查找可能对特定模块产生影响的参数:

a.使用模型切片器创建一个 SLSlicerAPI.ParameterDependence 对象。

slicerObj = slslicer('sldvexCommonCausesOfDeadLogic');

pd = slicerObj.parameterDependence;

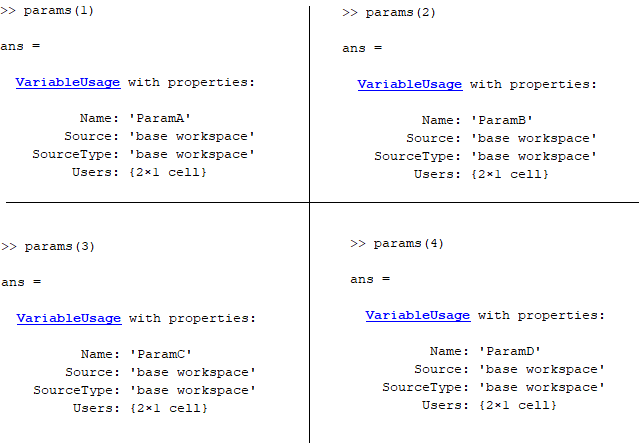

b.查找影响 Product 模块的参数。

params = parametersAffectingBlock(pd, 'sldvexCommonCausesOfDeadLogic/Parameters/Product');

上图显示了函数 parametersAffectingBlock 返回的参数,这些参数对 Product 模块有影响。可以考虑将该函数返回的参数列表用于调节。

c.执行清理以退出模型的编译状态。

slicerObj.terminate;