死逻辑的常见原因

导致模型中出现死逻辑的常见建模模式包括:

当您执行设计错误检测分析时,Simulink® Design Verifier™ 会在“结果”窗口中报告死逻辑的常见原因。

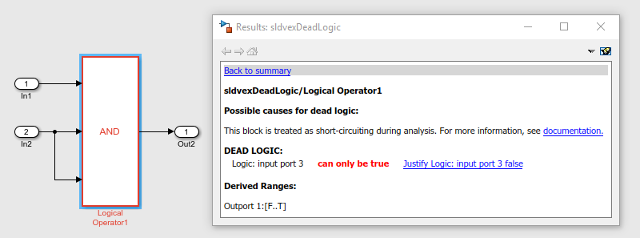

分析过程中 Logical Operator 模块的短路

Simulink Design Verifier 在分析死逻辑时会将逻辑模块视为短路。

例如,在此模型中,如果 In2 为 false,软件会由于短路而忽略第三个输入。“结果”窗口会将此端口列为死逻辑。请参阅逻辑运算短路。

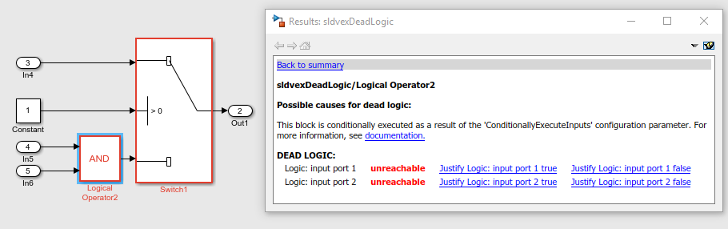

模块的条件执行

如果您的模型由 Switch 或 Multiport Switch 模块组成,并且条件输入分支执行参数设置为 On,则条件执行通常会导致意外的死逻辑。

假设有此示例模型,其中条件输入分支执行参数设置为 On。AND Logical Operator 模块基于条件执行,这会导致该模块出现死逻辑。有关详细信息,请参阅条件输入分支执行。

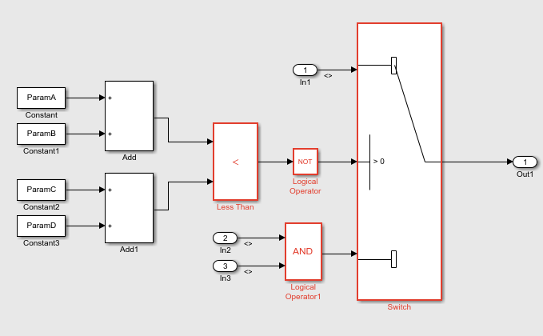

参数值被视为常量

如果您的模型包含参数,Simulink Design Verifier 会默认将这些参数值视为常量。这可能会导致模型中出现死逻辑。在这些情况下,可考虑将这些参数配置为在分析过程中可调整。

例如,假设有此模型,其中所有参数都设置为零。这些设置会导致 Less Than 模块出现死逻辑。

上游模块

当某个特定模块出现死逻辑时,通常会导致级联效应,从而使得下游模块也出现死逻辑。

参考上面的示例模型。Less Than 模块中的死逻辑会导致相应下游模块中出现死逻辑。因此,在检查任何下游死逻辑之前检查上游死逻辑通常会很有帮助。

库链接模块

库模块中可能包含一些防御性条件,这些条件在某些使用这些模块的位置是多余的。在某些情况下,这可能会导致死逻辑。请参阅排除并申述设计错误检测的目标。

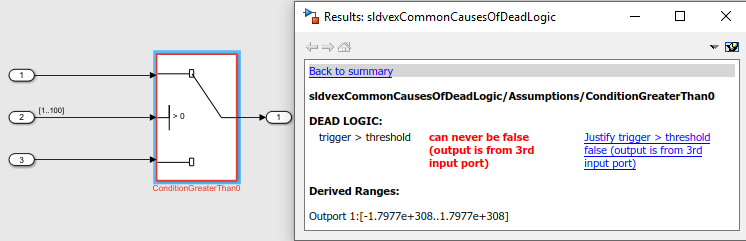

对信号范围的限制

在测试生成中,具有最小值和最大值约束的根级 Inport 模块以及 Test Condition 模块可能会导致死逻辑。例如,假设有 ConditionGreaterThan0 Switch 模块,其中第二个 Inport 模块的最小值和最大值范围分别为 1 和 100。这会导致该子系统中的 Switch 模块出现死逻辑。