Test Condition

限制测试用例中的信号值

库:

Simulink Design Verifier /

Objectives and Constraints

描述

Test Condition 模块定义了在测试生成模式下运行的模型中的信号的测试条件。(见Workflow for Test Generation)。使用值参数指定信号值的约束。该模块将指定的值参数应用于其输入信号并尝试生成测试用例。

您可以使用该模块来:

启用或禁用该条件。

指定模块是否应在 Simulink® 编辑器中显示其值参数。

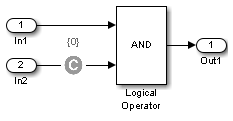

指定该模块是否应显示其输出端口。

当您使用 Simulink 和 Simulink Coder™ 生成代码时,Test Condition 模块将被忽略。Test Condition 模块在模型仿真期间不会修改信号,而仅使用该信号来生成测试条件。

端口

输入

输出

依赖关系

要启用此端口,请选择直通模式(显示输出端口)。

参数

扩展功能

版本历史记录

在 R2007a 中推出