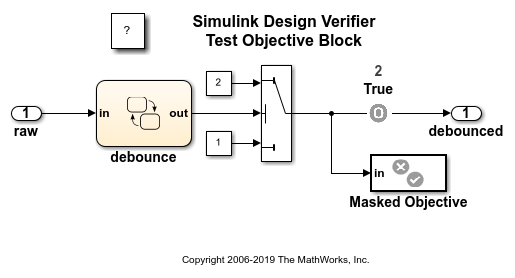

Test Objective

定义信号在测试用例中必须满足的自定义目标

库:

Simulink Design Verifier /

Objectives and Constraints

描述

在测试生成模式下运行时,Simulink® Design Verifier™ 软件会生成满足指定准则的测试用例(请参阅Workflow for Test Generation)。在这种模式下,您可以使用 Test Objective 模块为模型中的信号定义自定义测试目标。值参数允许您指定信号在测试用例仿真期间至少一个时间步长必须达到的值。该模块将指定的值参数应用于其输入信号,并且 Simulink Design Verifier 软件尝试生成满足目标的测试用例。

该模块的参数对话框还允许您

启用或禁用目标。

指定该模块应在 Simulink 编辑器中显示其值参数。

指定该模块应显示其输出端口。

注意

Simulink 和 Simulink Coder™ 软件分别在模型仿真和代码生成期间忽略 Test Objective 模块。Simulink Design Verifier 软件仅在为模型生成测试用例时使用 Test Objective 模块。

示例

端口

输入

参数

扩展功能

版本历史记录

在 R2007a 中推出