生成测试

生成测试用例集以实现模型和代码覆盖率并满足自定义测试准则

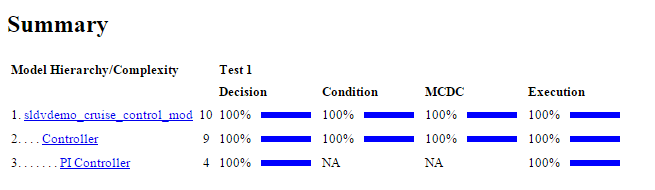

Simulink® Design Verifier™ 可自动生成测试用例,使您能够全面评估模型行为。测试用例通过演示模型中模块在不同模式下的执行情况,帮助您确认模型性能。生成测试用例时,软件会对模型进行形式化分析。分析完成后,软件会提供多种结果查看方式。有关详细信息,请参阅为模型生成测试用例。Simulink Design Verifier 通过生成测试用例,帮助实现模型覆盖率目标,例如修正条件/决策覆盖率 (MC/DC) 和边界值分析。此分析不仅可以增强模型的可靠性,还可以通过减少手动测试工作量来加快验证过程。生成的测试用例可用于对照指定的需求验证模型,确保符合行业标准并降低开发后期出错的风险。