使用时态逻辑扩展模型的测试用例

创建起始测试用例

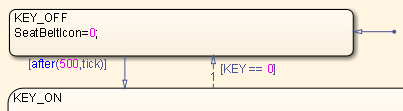

本例使用 sldvdemo_sbr_extend_design 模型。该模型包括一个使用时间逻辑的 Stateflow® 图 SBR。在 Stateflow 图仿真 500 次之后,会发生从 KEY_OFF 状态到 KEY_ON 状态的转移。要测试这种转移需要一个包含 500 个时间步的测试用例。

在此示例中,您创建一个测试用例,通过在测试用例的持续期内将 KEY_ON 输入设置为 KEY 来强制转移到 1。您使用此测试用例仿真模型,满足 KEY_OFF/KEY_ON 转移的目标。然后分析模型,忽略您创建的测试用例已经满足的目标。

打开示例模型:

openExample('sldv/DefiningExtendingExistingTestsCasesExample',... 'supportingFile','sldvdemo_sbr_extend_design');

打开

SBRStateflow 图查看KEY_OFF/KEY_ON转移。

创建模型参考框架模型:

[~, harnessModelFilePath] = ... sldvmakeharness('sldvdemo_sbr_extend_design',[],[],true);

框架模型

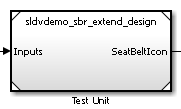

sldvdemo_sbr_extend_design_harness包括:一个名为“测试单元”的 Model 模块引用原始模型

sldvdemo_sbr_extend_design。

名为 Inputs 的 Signal Editor 模块包含 Model 模块中引用的模型的测试用例输入。

最初,Signal Editor 模块仅包含默认测试用例,所有三个输入都设置为

0。一个名为“Test Case Explanation ”的 DocBlock 模块,用于记录测试用例。

最初,测试用例解释模块不包含默认测试用例的任何内容。

sldvmakeharness返回harnessModelFilePath中的框架模型文件的路径。将框架模型文件的名称提取到harnessModel中,以供稍后使用:[~, harnessModel] = fileparts(harnessModelFilePath);

为了分析从 KEY_OFF 到 KEY_ON 的状态转移,创建一个测试用例,在 Signal Editor 模块中以 500 个时间步骤转移到 KEY_ON 状态。关闭 Signal Editor 模块。

记录启动测试用例

下一步是记录您创建的起始测试用例。然后,您可以指定 Simulink® Design Verifier™ 在执行分析时忽略该测试用例满足的目标。

sldvlogsignals 函数将测试用例数据记录在包含 sldvData 结构体的 MAT 文件中。该结构体存储了软件在分析过程中收集和产生的所有数据。

记录开始的测试用例:

保存引用

sldvdemo_sbr_extend_design模型的框架模型中的 Model 模块的名称:[~, modelBlock] = find_mdlrefs(harnessModel, false);

使用新的测试用例仿真 Model 模块仿真的模型,并将输入信号记录在工作区变量

loggeddata中:loggeddata = sldvlogsignals(modelBlock{1});将记录的数据保存在名为

existingtestcase.mat的 MAT 文件中:save('existingtestcase.mat', 'loggeddata');

当您分析

sldvdemo_sbr_extend_design模型时,您将指定此文件。

扩展现有测试用例

您现在可以分析 sldvdemo_sbr_extend_design 模型并指定分析扩展已经满足的测试用例。分析使用现有的测试用例数据作为起点,并且不会尝试为 SBR Stateflow 图中的 KEY_OFF 到 KEY_ON 的转移生成测试用例。

指定起始测试用例并分析模型:

打开模型。

open_system('sldvdemo_sbr_extend_design');在 Design Verifier 选项卡上,点击测试生成设置。

在“配置参数”对话框的测试生成窗格中,在针对缺失覆盖率添加测试下,选择使用现有测试数据进行扩展。

在测试数据字段中,输入包含记录数据的 MAT 文件的名称:

existingtestcase.mat

清除报告中的现有测试/覆盖率数据满足的单独目标.

当您清除此选项时,软件会将起始测试用例包含在最终测试套件中。您将看到完整的测试套件实现了 100% 的模型覆盖率。

要关闭“配置参数”对话框,请点击确定。

将

sldvdemo_sbr_extend_design模型保存在 MATLAB® 路径下,名称为sldvdemo_sbr_extend_design_test。点击生成测试。

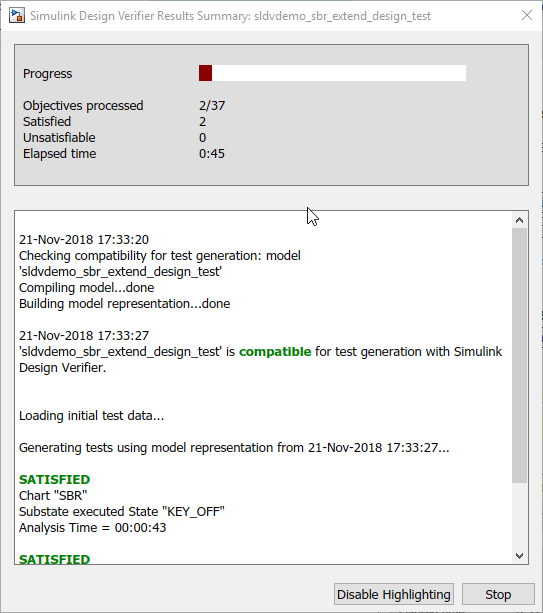

日志窗口首先列出起始测试用例满足的目标。

然后,日志窗口会列出除起始测试用例之外所生成的目标。

验证分析结果

为了确保此分析创建完整的测试套件,请生成框架模型,以便您可以使用生成的测试用例仿真该模型:

在 Design Verifier 选项卡的查看结果部分中,点击创建测试框架模型。

在框架模型

sldvdemo_sbr_extend_design_test_harness中,打开名为 Inputs 的 Signal Editor 模块。要使用所有测试案例对模型进行仿真,请点击全部运行并得出覆盖率按钮。

仿真完成后,将显示模型覆盖率报告。

查看

sldvdemo_sbr_extend_design_test模型的覆盖率信息,可以看到完整测试套件达到了 100%的覆盖率。