使用默认仿真为 Model 模块组件生成测试

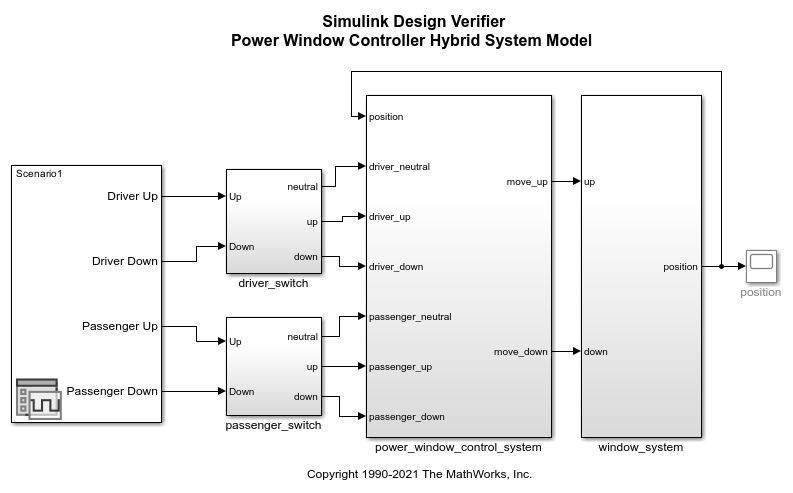

此示例说明如何使用 Simulink® Design Verifier™ 通过默认顶层模型仿真为 Model 模块生成测试用例。

此示例包含充当控制器的 Model 模块。顶层模型配置为被控对象在环仿真。您可以使用顶层模型仿真为控制器生成测试用例。

设置默认的被控对象在环控制器仿真

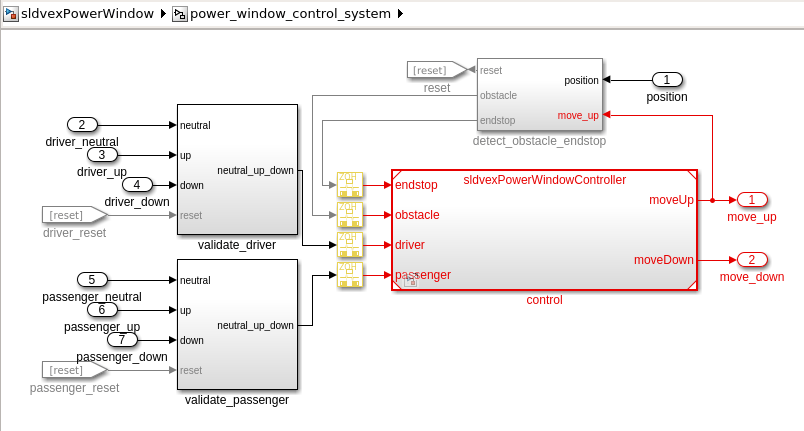

该模型包含一个电动车窗控制器和一个低阶被控对象模型。sldvexPowerWindow/power_window_control_system/control 是一个 Model 模块,它引用模型 sldvexPowerWindowController,该模型使用 Stateflow® 图实现控制器。

open_system('sldvexPowerWindow');

该模型在顶层包含一个 Signal Editor 模块。仿真设置为被控对象在环控制器仿真。

仿真顶层模型并为控制器生成测试用例

1.在 App 窗格中,打开 Design Verifier。

2.在分析部分中,点击“记住选择”图标以取消固定当前选择。

3.选择 Model 模块 sldvexPowerWindow/power_window_control_system/control。

4.在 Design Verifier 选项卡中,展开生成测试并点击仿真顶层模型并生成测试。

查看测试生成结果

Design Verifier 会运行默认仿真,以记录 Model 模块 sldvexPowerWindow/power_window_control_system/control 的输入。然后,Design Verifier 会对记录的输入运行测试扩展,以便为控制器生成额外的测试用例。

清理

关闭模型。

close_system('sldvexPowerWindow');