检测整数溢出错误

此示例说明如何使用设计错误检测分析来检测模型中的整数溢出错误。Simulink® Design Verifier™ 可以识别可能导致整数溢出的模型构造,然后证明整数溢出在仿真过程中不会发生,或者生成演示整数溢出错误的测试用例。

在此示例中,您将对模型执行设计错误检测分析,然后生成报告,显示哪些整数溢出目标是有效的,哪些目标导致了错误。

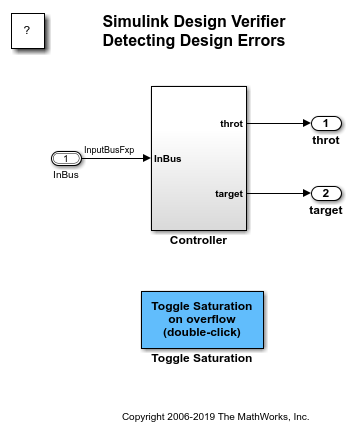

步骤 1:打开模型

在命令提示符下,输入:

open_system('sldvdemo_design_error_detection');

步骤 2:执行设计错误检测分析

模型已预配置为在“配置参数”对话框的 Design Verifier > 设计错误检测窗格中启用了整数溢出选项。

在 Design Verifier 选项卡上,点击检测设计错误。

软件会分析模型以检测整数溢出错误。分析完成后,“结果摘要”窗口报告五个目标有效,两个目标被证伪。

步骤 3:查看分析结果

要在模型上突出显示分析结果,请在“结果摘要”窗口中点击在模型上突出显示分析结果。有效的目标以绿色突出显示,证伪的目标以红色突出显示。

双击 Controller 子系统。点击以红色突出显示的 Sum 模块。结果检查器窗口会显示整数溢出目标。

要查看导致错误的测试用例,请点击查看测试用例。框架模型会打开,Signal Editor 模块会显示导致错误的测试用例。

步骤 4:修复整数溢出错误

对于发生整数溢出的两个 Sum 模块,启用对整数溢出进行饱和处理选项。或者,您也可以在 Simulink 编辑器中双击切换溢出饱和处理按钮。

要确认整数溢出错误已解决,请在 Design Verifier 选项卡中点击检测设计错误。分析完成后,软件会报告所有目标均有效。