Video Capture MIPI

Libraries:

SoC Blockset Support Package for AMD FPGA and SoC Devices /

MPSoC /

ZCU106

Description

Add-On Required: This feature requires the SoC Blockset Support Package for AMD FPGA and SoC Devices add-on.

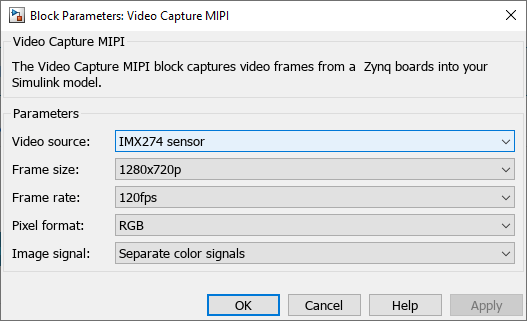

The Video Capture MIPI block captures video frames from an IMX274 FMC MIPI® CSI-2® card connected to a Zynq®-based board and imports the frames into your Simulink® model. The reference design programs the FPGA with an image that demosaics and gamma-corrects the video input from the sensor, and allows capture of the video from Simulink. You can control the frame size and Simulink video signal format options from the Video Capture MIPI block.

The FPGA image also contains an IP core called the FPGA user logic that you can generate from your design by using HDL Workflow Advisor. The block captures the input video after the FPGA user logic.

The video data is in AXI4-Stream Video format on the FPGA. When you import the video into Simulink, the stream converts to frame-based video.

The MIPI Receive path reference design requires the same video

resolution and color format for the entire data path.

The design you target to the FPGA user logic must not modify the frame size or format of the

data.

Examples

Limitations

To use this block, in the hardware setup, set Hardware Board to

Xilinx Zynq UltraScale+ MPSoC ZCU106 Evaluation Kitand set Add-on Card toIMX274MIPI-FMC.Use the IP core workflow to generate HDL code. This block does not support using the SoC Builder tool. For more information on workflows, see SoC Generation Workflows.

In the HDL Workflow Advisor tool, in step 1.1, set Target platform to

ZCU106 IMX274MIPI-FMC. In step 1.2, set Reference design toMIPI Receive path.You can also use the HDL Workflow Advisor to generate a software model for running in external mode.

Ports

Output

Parameters

Version History

Introduced in R2022b