Video Capture HDMI

Libraries:

SoC Blockset Support Package for AMD FPGA and SoC Devices /

MPSoC /

ZCU102

SoC Blockset Support Package for AMD FPGA and SoC Devices /

MPSoC /

ZCU106

SoC Blockset Support Package for AMD FPGA and SoC Devices /

Zynq-7000 /

PicoZed

SoC Blockset Support Package for AMD FPGA and SoC Devices /

Zynq-7000 /

ZC702

SoC Blockset Support Package for AMD FPGA and SoC Devices /

Zynq-7000 /

ZC706

SoC Blockset Support Package for AMD FPGA and SoC Devices /

Zynq-7000 /

ZedBoard

Description

Add-On Required: This feature requires the SoC Blockset Support Package for AMD FPGA and SoC Devices add-on.

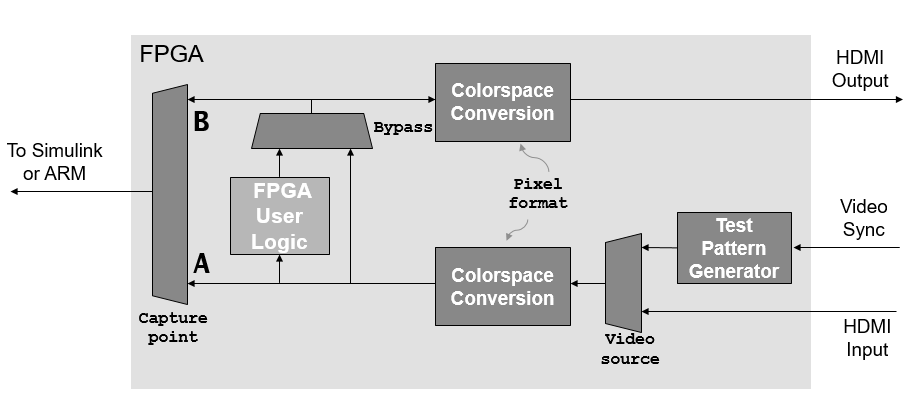

The Video Capture HDMI block captures video frames from a Zynq®-based board that has an HDMI FMC card, and imports the frames into your Simulink® model. The reference design programs the FPGA with an image that includes data path multiplexers, video format conversions, and a video test pattern generator (TPG). You can control these data path and conversion options from the Video Capture HDMI block.

Points A and B in the diagram show the options for capturing video into

Simulink or an ARM® processor. The FPGA user logic section is the IP core that you

generate from your design using HDL Workflow Advisor. You can capture the input video before the

FPGA user logic, or the output video after the FPGA user logic. If you enable the bypass of the

FPGA user logic, or if you have not generated any FPGA user logic, the two capture locations show

the same data.

The video data is a pixel stream on the FPGA, but when you import the video into Simulink, the stream converts to frame-based video.

The HDMI reference designs require the same video resolution and color format for the entire data path. The resolution you select for the Video Capture HDMI block must match that of your camera input. The design you target to the FPGA user logic must not modify the frame size or format of the data.

When you use this block in a model deployed with the default FPGA image, you can change the video format that the reference design captures to the ARM processor and therefore the format of the video frames imported to Simulink.

The HDL Workflow Advisor generates a software interface model that contains the Video Capture HDMI block. The parameter settings of the generated block match the settings of the Video Capture HDMI block in your original model. You can change the input video resolution, switch between HDMI input or an on-chip test pattern generator, and enable an optional bypass of the user logic section of the FPGA. When you change a parameter, the block writes an AXI-Lite register on the board.

You can also deploy this block to an ARM processor to capture the video from the FPGA user logic into the ARM for further processing. When you use the block this way, the settings on the block must match those of the deployed FPGA image.

To use this block in the generated software interface model, or to create your own model to target an ARM processor, you must have the Embedded Coder® product and the Embedded Coder Support Package for AMD SoC Devices.

Examples

Limitations

To use this block, in the hardware setup, set Hardware Board to one of the supported Xilinx® boards and set Add-on Card to

FMC-HDMI-CAM. You can find the supported boards in the Libraries list at the top of this page.Use the IP core workflow to generate HDL code. This block does not support using the SoC Builder tool. For more information on workflows, see SoC Generation Workflows.

In the HDL Workflow Advisor tool, select one of these supported platforms and one of these supported reference designs.

Target Platform Reference Design ZCU106 FMC-HDMI-CAMZCU102 FMC-HDMI-CAMPicoZed FMC-HDMI-CAMZC702 FMC-HDMI-CAMZC706 FMC-HDMI-CAMZedBoard FMC-HDMI-CAM

RGBY onlyYCbCr 4:2:2RGB AXI4-Stream Video InterfaceY only AXI4-Stream Video InterfaceYCbCr 4:2:2 AXI4-Stream Video Interface

You can also use the HDL Workflow Advisor to generate a software model for running in external mode.

Ports

Output

Parameters

Tips

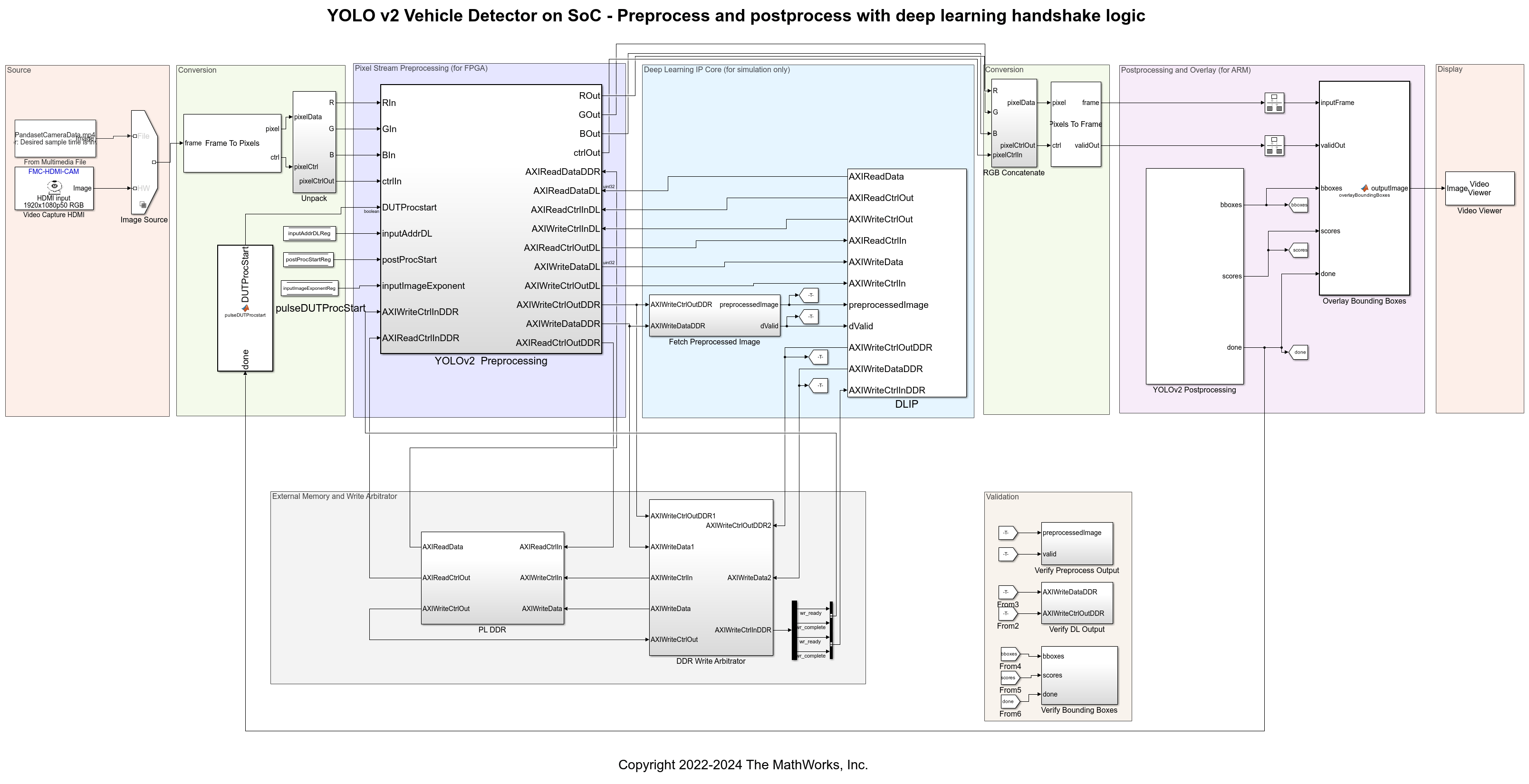

When you use the RGB with DL Processor reference design, you can

deploy the design and then open a simple capture model, such as the Getting Started with Vision Zynq Hardware

model, to capture video while the design runs on the board. The video captured is the result of

the postprocessing operation in the ARM processor. To capture video from this reference design, set the Video

Capture HDMI block parameters to these values.

Video source must be

HDMI input. This reference design does not contain a test pattern generator.Frame size must be

1080p HDTV (1920x1080p).Pixel format must be

RGB.The Bypass FPGA user logic and Capture point parameters have no effect with this reference design.

For an example, see YOLO v2 Vehicle Detector with Live Camera Input on Zynq-Based Hardware (Vision HDL Toolbox).

Version History

Introduced in R2023a