Getting Started with Vision Zynq Hardware

This example shows how to get started with video capture and processing using SoC Blockset™ Support Package for AMD® FPGA and SoC Devices.

This example tests the data path from the Zynq® device to the host by configuring the board to transmit a test pattern that is captured and displayed in Simulink®. The test pattern input is available only with the reference designs for the HDMI FMC card. To set up a board that has a MIPI sensor, see Getting Started with MIPI Sensor.

Setup

Before running this model, your hardware must be set up and connected to the host machine running Simulink. Install SoC Blockset™ Support Package for AMD® FPGA and SoC Devices and run the guided hardware setup included in the support package installation. The setup tool configures the target board and host machine, confirms that the target starts correctly, and verifies host-target communication.

For more information, see Install Support for AMD FPGA and SoC Devices and Set Up AMD FPGA and SoC Devices.

Live Video Capture from Target

The main purpose of this example is to check that the target development board has been set up correctly, and that it can communicate with the host platform.

open_system('vzGettingStarted');

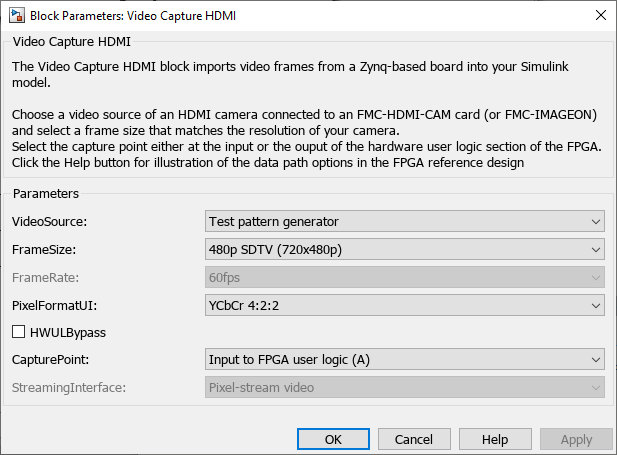

The Video Capture HDMI block receives captured image data from the target hardware and imports it into Simulink as source data for simulation. The Block Parameters allow you to configure the format of the captured data using the target hardware. The block is configured as shown.

These parameters specify:

A Video source of

Test pattern generator. The Test Pattern Generator (TPG) is situated in the FPGA fabric of the Zynq device, and allows a known test pattern to be transmitted as a video source.A video frame size of

480p SDTV (720x480p). This is the smallest frame size supported by the hardware.A video frame rate of

60fps.A pixel format of

YCbCr 4:2:2(otherwise known as YUYV). This parameter controls the format of the video frames delivered on the output ports. Other support pixel formats are Y only, and RGB.A Capture point of

Input to FPGA user logic (A). Frames are captured and sent to Simulink from the input of the FPGA user logic.Bypass FPGA user logic is

unchecked. This is the default option.

The To Video Display block displays the video frames received by the Video Capture HDMI. The block is configured to display frames in YCbCr 4:2:2 (YUYV) format. It can also be configured to display RGB frames. If you require to display frames in Y only format, you can use the Video Viewer block from the Computer Vision Toolbox/Sinks library.

The Frame Rate Display block displays the video frame rate of the simulation in relation to wall clock time, i.e. frames per second.

Running the Example with Test Pattern Generator (TPG)

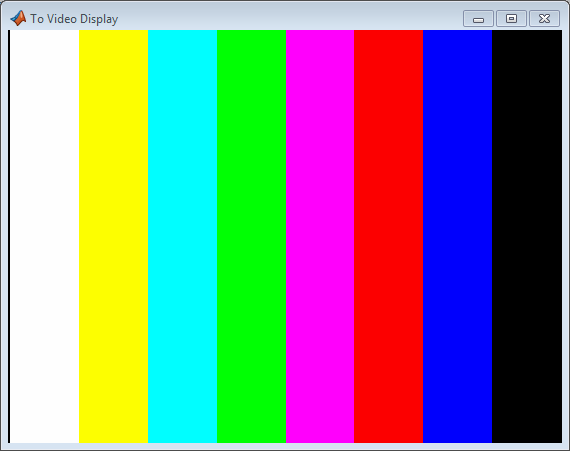

This example is configured to generate a test pattern with a frame size of 480p. When you run the simulation, the Captured Image Display scope opens. You should see the test pattern as shown.

If you connect an HDMI display to the HDMI Out port of the FMC-HDMI-CAM card, you should see the same test pattern.

Running the Example with HDMI Source

If you have an external HDMI source, such as a camera, you can use that as the video source for this model. To use an external HDMI source, follow these steps:

Connect the HDMI source to the HDMI In port of the FMC-HDMI-CAM card.

Configure the Video Source parameter of the Video Capture HDMI block to

HDMI input.Configure the Frame size parameter of the Video Capture HDMI block to match the output frame size of your source.

Run the model.

You should now see live video frames from your HDMI source displayed in the To Video Display window, and the HDMI display on the FMC board (if connected).

Next Steps

You have used this model to confirm your hardware setup and connection to Simulink. Next, see Developing Vision Algorithms for Zynq-Based Hardware.