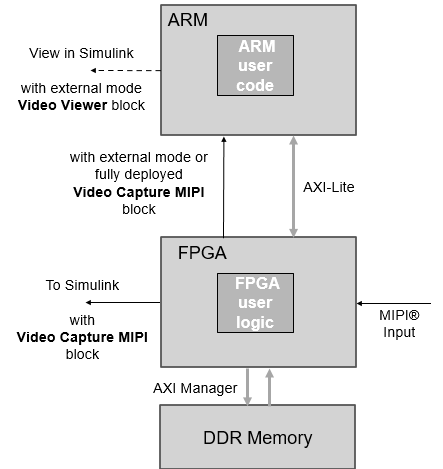

Zynq Video Dataflow for MIPI Input

SoC Blockset™ Support Package for AMD FPGA and SoC Devices assists you in targeting designs to the FPGA and ARM® processor on the Zynq® board. This page explains data path options for moving the video data between the FPGA, external memory, the ARM processor, and the Simulink® host computer, when your board is connected to a MIPI® CSI-2® FMC card. The MIPI add-on card is supported only with the ZCU106 board.

The Zynq board receives input video through an FMC MIPI module. The video data flows through the FPGA, including your customized FPGA user logic. The FPGA user logic can include an AXI manager interface for random memory access. You can optionally export the video data to Simulink, or route it to the ARM processor. The video data is in streaming pixel format on the FPGA. When you import this video data to the ARM processor or Simulink, it is converted to frames.

Capture to Simulink

To capture frames to Simulink from the FPGA, use the Video Capture MIPI block. Get started by selecting one of these models that include the Video Capture MIPI block:

Example model for pixel streaming. See Corner Detection with Zynq-Based Hardware and MIPI Sensor and Single-Pixel Streaming from MIPI Input.

Generated hardware interface model from HDL Workflow Advisor. This model also includes a Host AXI Interface block, with ports to read and write the AXI-Lite registers on the FPGA. See Models Generated from FPGA Targeting.

External Memory Interfaces

SoC Blockset Support Package for AMD FPGA and SoC Devices provides a simplified external memory interface model for simulation. For deployment, map this interface to the provided memory interface of the reference design. When you use a MIPI CSI-2 FMC card, you can use the AXI manager interface to read and write any address in the external memory. The memory interface does not maintain streaming video control signals.

Capture to ARM Processor

To route video to the ARM processor, use the Video Capture MIPI block. You can run this block in external mode or and fully deploy it to the ARM processor. Get started by selecting one of these models:

New model. When you generate code for the ARM processor, it runs alongside the default FPGA image loaded at setup. You can change the video format of the captured data using the parameters on the Video Capture MIPI block.

Generated software interface model from HDL Workflow Advisor, after you load your custom FPGA logic to the board. This model already includes the Video Capture MIPI block. The pixel format parameters match the video format settings on the FPGA and are informational only. This model also includes a Xilinx Zynq AXI Interface block, with ports to read and write the AXI-Lite registers on the FPGA. See Models Generated from FPGA Targeting.

In either of these models, you can view the modified video frames in Simulink by running the Video Viewer block in external mode.